# パルス波高値計測回路の製作

# 吉田久史、○豊田朋範

自然科学研究機構 分子科学研究所 装置開発室

# 概要

分子科学研究所の極端紫外光実験施設(UVSOR)の自由電子レーザー(FEL: Free Electron Laser)実験において、FEL 強度モニターからの信号の波高値を計測する装置が必要になった。信号の波高値は最終的に TDC(Time to Digital Converter)によりパソコンに取り込むため、製作する計測装置には波高値の検出と同時にその値に比例したインターバルを持つ 2 つのパルスを出力する機能が必要となった。我々は、40MSPS の 12bitA/D 変換器と Xilinx の CPLD を使用して、それらの機能を順次実行する計測装置を製作した。本報告では回路ブロックの機能とハードウェア記述言語による構築、並びにシミュレーションによる動作検証手法等について報告する。

# 1 計測装置の構成

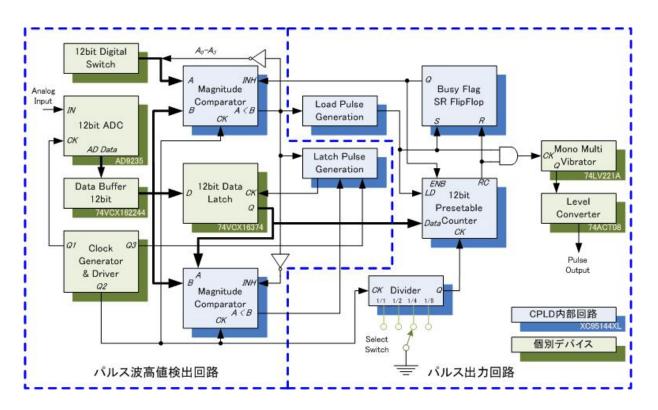

本装置の回路構成を図1に示す。CPLDで構築したのは図1における青色の部分である。CPLDで構築した理由は、(1)40MHzの高速クロックに同期したシーケンス動作を実現する(2)NIM1 巾モジュールという限られたスペースに実装する-の2つが挙げられる。シーケンス動作については別記事で詳述されているので、ここでは割愛する。

図1. パルス波高値計測回路のブロック図

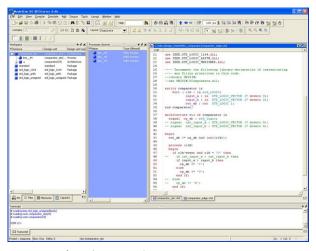

CPLD の機能を構築するには、ハードウェア記述言語が用いられる。今回は筆者が何度か製作経験を有する $^{[1]}$ Xilinx 社の IDE(統合開発環境)である ISE Webpack と、XC95144XL-10TQ144 $^{[2]}$ を搭載したカメレオン USB 基板 $^{[3]}$ (図 2)を用いた。ハードウェア記述言語は VHDL を選択した。

# Capheleon USB UZ.82

図 2. カメレオン USB

## 2 VHDLによるディジタル回路構築

# 2.1 マグニチュード・コンパレータ

12bitA/D 変換器 AD9235<sup>[4]</sup>は、40MHz のシステムクロックに同期して、12bit ディジタルデータを逐次出力する。図 1 上段のコンパレータ(コンパレータ 1)は、この 12bit ディジタルデータ B とスイッチで設定するしきい値 A を比較して、A<B の時出力を"1"にする。図 1 下段のコンパレータ(コンパレータ 2)は、ラッチされたデータ A と 12bit ディジタルデータ B を比較して、A<B であれば出力を"1"にする。いずれのコンパレータもシステムクロック CK の立ち下がりで比較判定する。また、INH 入力が"1"だと比較動作を停止して出力を保持する。

コンパレータ1のVHDLソースを図3に示す。比較演算のために2つの入力をbit列からIntegerに変換する(241-246行)。クロックもしくはINHの変化で駆動するprocess 構文(250-265 行)では、INHが"1"であれば直前の出力を保持する(252-255行)。INHが"0"であれば、クロックの立ち下がりで比較演算を行う。しきい値より12bitディジタルデータが大きければ出力を"1"にして、小さければ"0"にする。それ以外では出力を"0"にする(257-263 行)。

図 3. コンパレータ 1 の VHDL ソース

### 2.2 12bit プリセッタブル・ダウンカウンタ

TDC に接続する出力パルスのインターバルを生成する 12bit プリセッタブル・ダウンカウンタは、ロード入力LD が"0"の時に 12bit ラッチデータData をプリセット値とする。イネーブル入力 ENB が"1"であればクロック CK の立ち上がりでダウンカウントする。カウント値が 0 になるとキャリー出力 RC を"0"にする。

12bit プリセッタブル・ダウンカウンタの VHDL ソースを図 4 に示す。

図 4.12bit プリセッタブル・ダウンカウンタの VHDL ソース

後述の分周器で分周されたシステムクロックかロード入力かイネーブル入力のいずれかの変化で駆動する process 構文(217-225 行)では、ロード入力が"0"であればパルス波高値をプリセット値としてロードする。イネーブル入力が"1"の時、クロックの立ち上がりで1つダウンカウントする。カウンタの値の変化で駆動する process 構文(228-234 行)では、カウンタの値が0且つイネーブル入力が"1"の時にキャリー出力を"0"に、その他の状態では"1"にする。

#### 2.3 分周器(Divider)

12bit プリセッタブル・ダウンカウンタに供給するクロックを生成する分周器は、入力されるシステムクロック CK を 1/1、1/2、1/4、1/8 分周し、

外部スイッチで選択した分周値のクロックを出力する。

分周器の VHDL ソースを図 5 に示す。システムクロックと 4bit 分周値入力で駆動する process 構文において、システムクロックの立ち上がりで 1 つアップカウントする 4bit カウンタを構成する(169~176 行)。また、4bit 分周値入力の値に応じて、出力をシステムクロックもしくは 4bit カウンタのいずれかの bit に接続するセレクタ回路を構成する(179-191 行)。

分周値入力が想定する 4 つ以外の場合、出力が不定になる恐れがある。それを回避するため、セレクタ回路で現在の分周値を示すフラグint\_flagdivを設定しておく。分周値入力が想定以外の値では、int\_flagdivの値に応じて出力をシステムクロックもしくは 4bit カウンタのいずれかのbit に接続する(192-203 行)。

```

166|>

---Abit_Selectable_Divider_---

--_Abit_Selectable_Divider_---

--_Dividing_section_---

process_(clk,div_selin)_begin---

> if_(clk'event_and_clk_--'!')_then---

> if_(int_divcnt_--''1111')_then---

> int_divcnt_<--'0000":--

167

168

169

170

171

172

173

174

int_divent_<=_int_divent_+_ '1';

175

176

177

end_if;

end if;←

Seleting (pre) output section م

case (div_selin) is م

when "1110" => م

178

179

180

pre_divout_<=_clk;-

int_flagdiv_<=_0;> --_Select_'clk'(1/1_dividing)-

182

> pre_divout <= _int_divent(0);

> int_flagdiv_<=_1:> --_Select_1/2_dividing when_"1011" => \div

183

184

186

predivout

int_flagdiv_<=_int_divcnt(1);4

int_flagdiv_<=_2;5 --_Select_1/4_dividing4

n_"0111"_=>4

187

188

> pre_divout_<=_int_divont(2);d

> int_flagdiv_<=_3;> --_Select_

when_others_=>d

190

--_Select_1/8_dividing←

191

192

case_(int_flagdiv)_ise

when_0_=>e

194

pre_divout <= clk;←

195

> pre_divout_<=_int_divcnt(0); dwhen_2_=>d

196

> pre_divout_<=_int_divent(1); dwhen_3_=>d

198

199

200

201

pre_divout <= int_divcnt(2);</pre>

201 | 3

202 | 3

203 | 3

204 | 3

205 | 4

206 | 3

207 | 3

end_case; ←

int_flagdiv_<=_int_flagdiv;

end case;

end_process;←

```

図 5.分周器の VHDL ソース

#### 3 シミュレータによるディジタル回路の動作検証

試作したカメレオン USB(CPLD)の動作検証では、ファンクション・ジェネレータや外部スイッチ回路を基板に接続し、入力条件を変化させてその応答を観測する手法を取る。ハードウェア記述言語で構成したディジタル回路はソースの変更で容易に回路構成を変更できるが、そのたびに前述の手法で動作検証を繰り返すのは非効率的である。また、観測したい信号線はすべて CPLD の I/O ピンを通して外部に引き出す必要がある。今回は従来の手法に加えて、シミュレーションによるパソコン上での動作検証を行った。

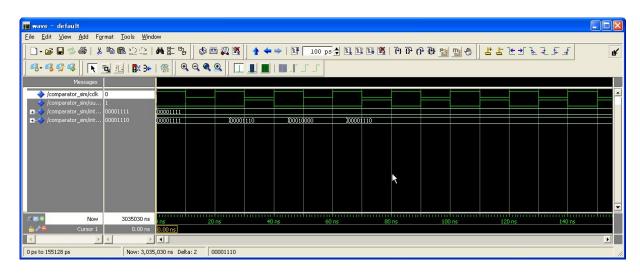

シミュレータには、Xilinx 社から無償提供されている ModelSim(図 6)<sup>[5]</sup>を用いた。電子回路シミュレータでは Spice が有名であるが、ModelSim も回路に入力する信号を定義してその出力を検証するツールである。Spice では回路構成を示すファイルであるネットリストをテキストエディタや回路図エディタで作成するのに対し、ModelSim は入力信号を定義するテストベンチと称するテキストファイルと、同じくテキストファイルである検証対象のVHDL(もしくは Verilog-HDL)ソースを使用する。

今回製作したマグニチュード・コンパレータについてのテストベンチを図7に示す。テストベンチは

図 6. ディジタル回路シミュレータ ModelSim

VHDL もしくは Verilog-HDL の文法を使用する。図 9 は VHDL の文法を使用したもので、まずライブラリを 読み込み(6-9 行)、回路モジュールを定義する(12-17 行)。 続いて回路モジュールの入出力を定義して(21-27 行)、 内部信号の定義や(29-32 行)信号の振る舞い(45 行-)を記述する。

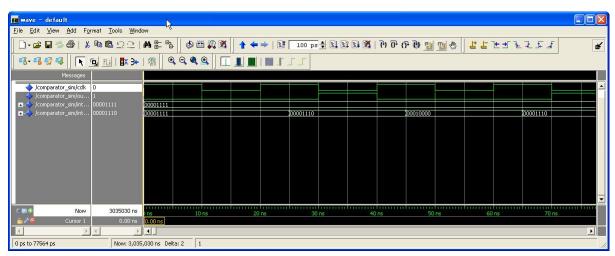

図 7 のテストベンチをシミュレーションした結果を図 8-1 と 8-2 に示す。波形は上から順にシステムクロック、出力、データ入力 B である。A>B が成立する時、システムクロックの立ち下がりで出力が"1"になり、システムクロックの次の立ち上がりで"0"になる出力が得られている。このように、テストベンチを使用することで、あたかも各種外部入力を接続してロジックアナライザを使用しているように回路の入出力を表示・検証できる。

```

H C:/Xilinx/design_sheet/MAG_Comparator/comparator_sim.vhd

<u>F</u>ile <u>E</u>dit <u>V</u>iew <u>T</u>ools <u>W</u>indow

Ln#

-- Module Name:

comparator - rtl - simulation file

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

10

entity comparator sim is

Port (clk: in std LOGIC;

input_a: in STD_LOGIC_VECTOR (7 downto 0);

input_b: in STD_LOGIC_VECTOR (7 downto 0);

out_ab: out STD_LOGIC);

13

16

end comparator_sim;

architecture rtl of comparator sim is

20

component comparator

port (

clk : in std_LOGIC;

input a : in STD_LOGIC_VECTOR (7 downto 0);

input b : in STD_LOGIC_VECTOR (7 downto 0);

out_ab : out_STD_LOGIC_);

22

23

26

signal cclk : std_logic;

signal out_ab : std_logic;

signal int_input_a : STD_LOGIC_VECTOR (7 downto 0);

signal int_input_b : STD_LOGIC_VECTOR (7 downto 0);

29

32

33

34

35

U: comparator

port map (

clk => cclk,

out_ab => out_ab,

input_a => int_input_a

input_b => int_input_b

36

37

38

39

40

41

42

43

44

45

46

47

48

begin

int input a <= "00001111";

int input b <= "00001111";

cclk <= 'I'; wait for 10ns;

cclk <= '0'; wait for 10ns;

49

cclk <= '1'; wait for 5ns;

int_input_b <= "00001110"; wait for 5ns;

cclk <= '0'; wait for 10ns;</pre>

51

53

54

55

cclk <= '1'; wait for 5ns;

int input h <= "000100000" wait for 5ns

Ln: 19 Col: 0 READ

```

図 7.マグニチュード・コンパレータのテストベンチ

図 8-1. ModelSim でのシミュレーションの様子(1)

図 8-2. ModelSim でのシミュレーションの様子(2)

#### 4 総括

CPLD を用いることで、標準ロジック IC では実現が難しい特別な機能を有するディジタル回路を VHDL により柔軟に構築できた。また、シミュレーションを導入することで動作検証をより効率的に行えた。

複数の回路ブロックを同時に駆動させたため、ある回路ブロックの出力論理のミスが回路全体に波及して動作に支障をきたす事態に遭遇した。複数の回路ブロックを正確に動作させるためには、ソースの一部を修正するにしても常に回路全体の動作を俯瞰する必要性があると実感した。

#### 参考文献

- [1] 豊田朋範、河本充司、"USB 接続 NMR 用高速高分解能データロガーの開発"、平成 20 年度京都大学総合技術研究会報告集第一分冊、平成 20 年 3 月、p190-191

- [2] XC95144XL Data Sheet, Xilinx Inc.

- [3] http://optimize.ath.cx/cusb/index.html

- [4] AD9235 Data Sheet, Analog Devices Inc.

- [5] 芹井滋喜、黒毛利 学、"はじめよう!ディジタル回路シミュレーション"、トランジスタ技術 2003 年 5 月号別冊付録、平成 15 年 5 月