# 中性子散乱実験用 位置敏感検出器、PSD2K システムの開発

佐藤節夫

高エネルギー加速器研究機構

物質構造研究所、中性子科学研究施設

〒305-0801 茨城県つくば市大穂 1-1

## 概要

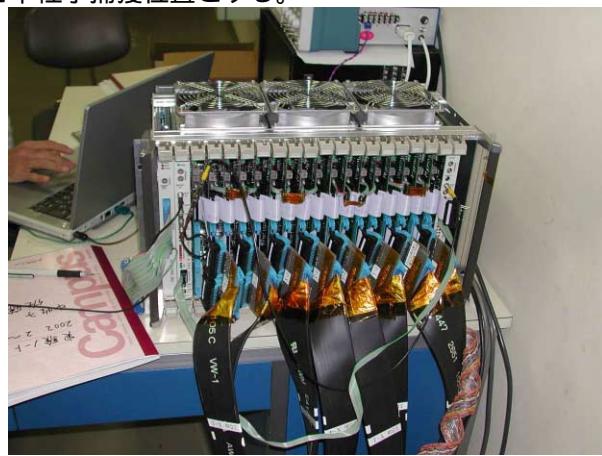

中性子散乱実験用の、中性子の到達位置と時刻を検出できるシステムを開発した。処理方式をアナログ方式からデジタル方式に変え、位置の分解能が 7mm から 4mm に改善された。写真 1 に開発を行なった PSD2K システムの中性子検出器（手前 8 本の円筒）と処理回路部分の写真を示す。

このシステムの処理回路部分に、再プログラミング可能なゲートアレイを使用したため、他のシステムへの応用が容易になった。ゲート数の余裕も十分にあり、ハードウェアの変更無しに、いろいろな機能が実現できた。

写真 1 PSD2K システム

## 1. はじめに

中性子科学研究施設においては、多くの PSD (Position Sensitive Detector: 位置敏感型検出器) を使用した実験装置が、1980 年から現在までに建設されてきた。第一世代は小角中性子散乱装置、SAN 用のもので、PSD を 43 本使用したシステムである。このシステムは外注で設計・製作を行なった。現在は使われていない。

第二世代は 1990 年から 1993 年に開発を行なった粉末結晶解析装置、VEGA 用のもので、PSD を 250 本使用したシステムである。VME システムと位置の計算用に、VME ボードコンピュータを採用した（文献(3)参照）。現在、PSD 約 150 本分が稼動中である。

第三世代は 1994 年から 1997 年に開発を行なった高分解能粉末結晶解析装置、SIRIUS 用のもので、PSD

を 500 本使用したシステムである。パーソナルコンピュータを、VME ボードコンピュータの代わりに採用し、位置の計算をさせた（文献(2)参照）。現在、PSD 約 500 本分が稼動中である。

この PSD2K システムは第四世代に相当し、1998 年から開発している。検出器信号を増幅した直後の出力を ADC (アナログ-デジタル変換器) で変換し、これ以降の PSD 処理を完全にデジタル化し、高密度、高速、低価格を追求した。このシステムは、中性子の強度が 2 桁以上高くなると予想される、将来計画に向けて開発しているものである。

当初、PSD98 システムとして開発したが、改良し、

PSD2K システムとした。基本方式、位置分解能はほぼ同じであるが、処理速度が飛躍的に改善されたのと、製作方式が簡略化され、維持管理もしやすくなった。

2002 年 3 月現在の中性子科学研究施設では、SWAN グループで PSD 約 120 本分の PSD98 システムが稼動中である。また、MRP グループで 32 本分の PSD2K システムが稼動中である。ARISA グループで PSD2K システムのテスト中である。

SIRIUS グループで約 250 本分の PSD2K システムが稼動し始めた。

## 2. PSD2K システムの開発の動機

1990 年ごろから PSD の開発を行なっていて、第三世代の SIRIUS 用の PSD で開発をやめるにはあまりに問題点が多かった。500 本の PSD を前に、1 本 1 本丹念に調整していく感じたことは次のようなことである。

- 1 : 精度を上げるための調整箇所が多すぎる。

- 2 : アナログ処理で、いくつものアンプ、フィルターを通すため、高品質が得にくい。

- 3 : 部品メーカーによる供給停止部品が多く、維持管理が困難。

そこでこれらを解決すべき方法として、デジタル処理ができないかを模索した。幸いにも、時代がデジタル処理に向かっていたので、次のように解決できることがわかった。

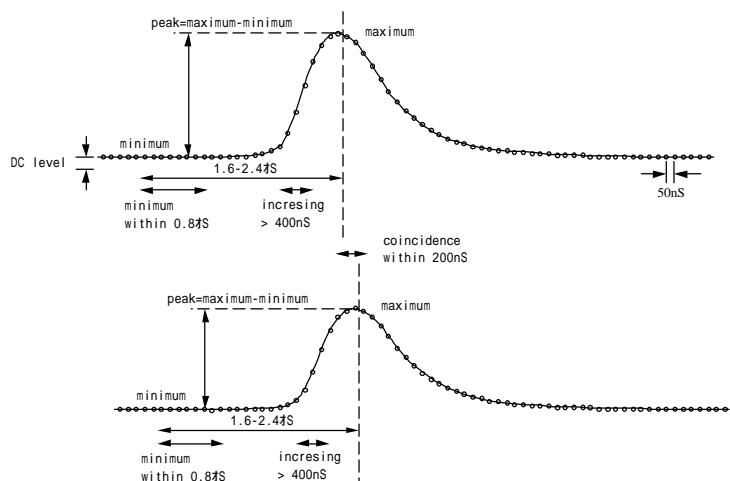

- 1 : 信号のみで、正確に波高値のピークが求められるため、調整が不要 ( 7 項、図 1 1 参照 ) 。

- 2 : デジタル値にしてしまえば、有効桁数の確認だけで、劣化しない。

- 3 : 世の中の流れがデジタルで、供給停止部品は少ない。

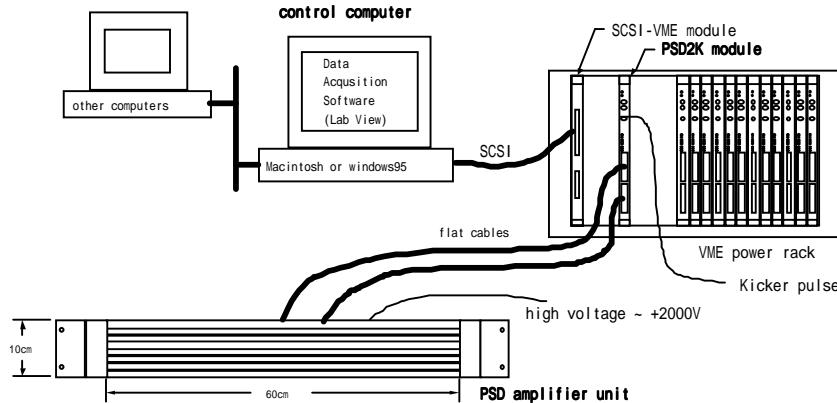

図 1 PSD2K システムの基本構成図

デジタル化したお陰で、さらに次の点が改善された。

- 1 : 位置の分解能が 7mm から 4mm に向上。

- 2 : 一枚幅のダブルハイイトの VME ボードで処理できる PSD の数が、4 本から 8 本に増え、高密度化。

- 3 : 64 位置分解能\*8K 時間分解能、128\*4K、256\*2K が選択可能 ( 16M バイトメモリ ) 。

- 4 : 1 中性子当たり、0.5  $\mu$  秒の処理能力。

- 5 : 各 PSD の設定値、スケール、オフセット、バランス等を EEPROM に記録できる。

- 6 : データの高速転送用に FIFO バッファを持つ ( ワルトラ SCSI 使用で、8M バイト / 秒 ) 。

- 7 : 低価格で PSD1 本あたりの価格が 4 万円程度。

図 1 に、このシステムの基本構成図を示す。PSD 支持箱( 図中、PSD amplifier unit ) PSD2K モジュール、制御用コンピュータからなる。PSD 支持箱は 8 本の PSD を保持し、PSD 出力を増幅する。PSD2K モジュールは PSD 支持箱から信号を受け、位置を計算し、飛行時間の情報を合わせて、ヒストグラムを作り出す。制御用コンピュータは PSD2K モジュールの初期設定と、ヒストグラムデータの読み出しを行なう。

### 3 . データ処理の概要

使用する PSD は Reuter-Stokes 社製の RS-P4-0424-206 である。形状は直径 12.7mm(0.5 インチ)、有効長約 60cm のステン

レス製の円筒で、芯線抵抗は約 4K オームである。中性子の測定には円筒を接地(0V)にし、芯線に 1400 ~ 2000V の高電圧を加えて、ガス増幅をさせて使用する。

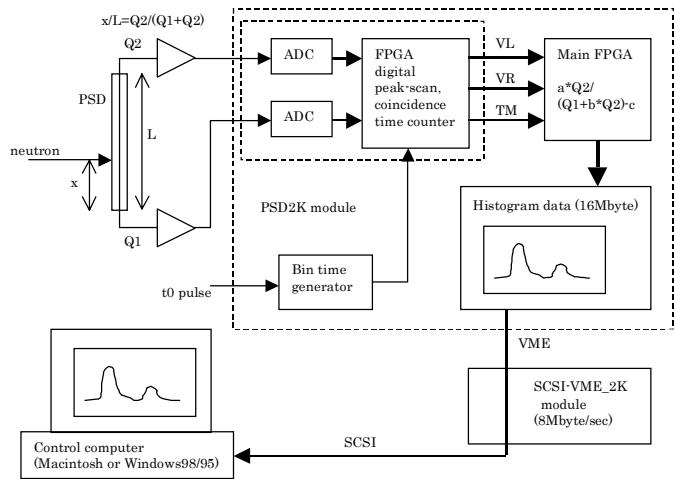

図 2 にデータ処理のブロック図を示す。PSD の全長を L、到達点を x、両端に出てくる電荷量をそれぞれ Q1、Q2 とすると、 $x/L = Q2/(Q1+Q2)$  の関係式になる( 抵抗分割法 )。PSD 支持箱は電荷 Q1 と Q2 を電荷感応型アンプで電圧に変換し、これらの電荷に比例した波高電圧を持つパルスにして、外部に送りだす。

この信号を PSD2K モジュールで解析処理を行なう。PSD2K モジュールは P12vir カード 4 枚と PSD2K-VME ボード 1 枚で構成される、1 枚幅 VME モジュールである。1 枚の P12vir カードで 2 本の PSD の波高値と到達時間を記録する。これらのデータを PSD2K-VME ボードが集め、プログラムブル・ゲートアレイで  $Q2/(Q1+Q2)$  を計算し、それぞれの中性子の捕獲位置を求める。次に、相当するヒストグラムメモリ上に蓄積していく。

これらの処理はパイプライン

方式で、並列に行なわれる。1 中性子データ当たり、0.5  $\mu$  秒で計算・蓄積できるので、8 本の PSD から同時にデータが来ても、4  $\mu$  秒で処理できる。そのため、処理速度が一定になるように、各入力で 4  $\mu$  秒のデッドタイムを設定した。

ヒストグラムデータは、制御用コンピュータからの要求があれば、測定の合間に、いつでも最新データを送りだすことができる。制御用コンピュータは PSD2K モジュールの初期設定、および制御を行ない、最終的にデータの読み出し、保存をする。制御プログラムは NATIONAL INSTRUMENTS 社の LabVIEW で作成した。このため、Macintosh と Windows98/95 上で、同じ環境で使用できる。

図 2 PSD2K システムのデータ処理ブロック図

## 4. 完全デジタル化によるデータ改善

### 4.1 一様性

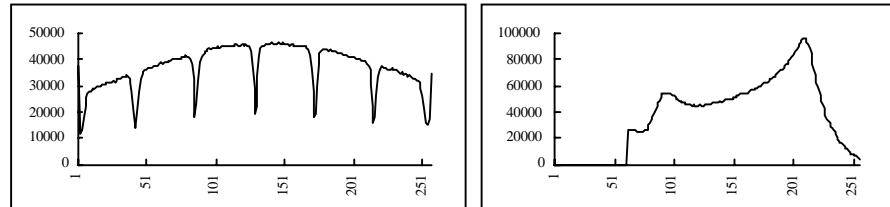

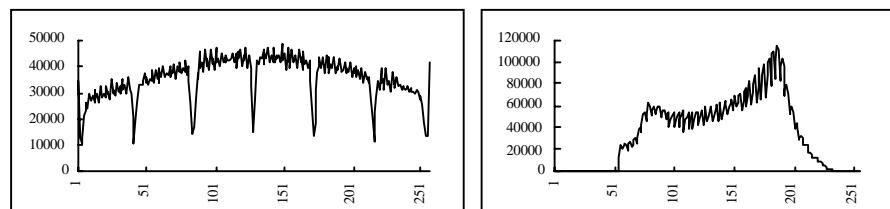

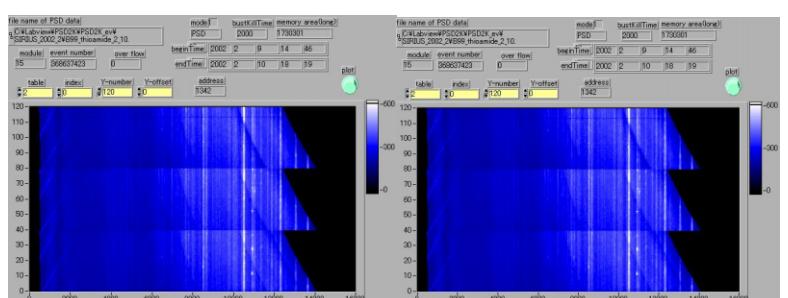

図3、4にPSD2Kシステムと古いシステム(第三世代のシステム:アナログ処理)のデータを示す。両方とも同じ条件にして測定を行なった。PSD支持箱にカドミウムの5mm幅の棒を取り付け、その影を観測した。上4本をPSD2Kシステムで、下3本を古いシステムで測定した。パルス中性子源を使用し、5ミリ秒のバーストパルスをカットし、50cm離れた距離で測定した。

位置の分解能、直線性に違いは見られないが、古いシステムのばらつきが、統計以上であるのがわかる。これは、位置、波高値を求めるADCの特性が、そのまま出てきている。主な原因は、このADCがハーフフラッシュタイプで、6ビット-4ビットで10ビットの精度を出しているが、前変換の6ビットが支配的である。さらに、この変換を、割算の代用として使うため、リファレンスをも変動させて使用するので、あまり良い特性が出ない原因の一つでもある。しかし、6ビット精度で使用するのには、あまり問題になつていなかつた。

これに対し、PSD2Kシステムでは、始めに12ビットADCでデジタル化し、後は計算だけで求めるので、ほとんど統計誤差だけになる。特に、ADCの使用方法に無理がないため、良い特性が得易い。これにより、新システムでは、より信頼性の高いデータが得

図3 PSD2Kシステムの位置データと波高値データ

図4 古いシステム(SIRIUS)の位置データと波高値データ

図5 PSD2Kシステムの位置データと波高値データ(1950V)

られることが期待できる。さらに、高精度の位置の分解能を必要とする実験にも使用できる可能性がある。

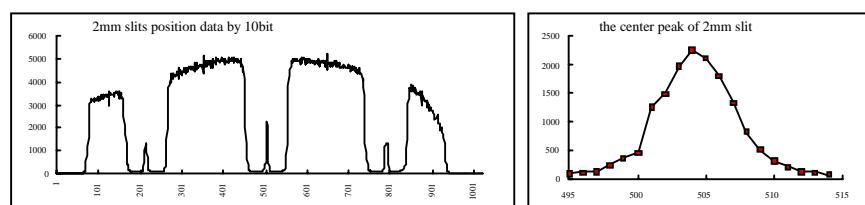

### 4.2 半値幅

次に位置の分解能が、良くなつたことを見るために、2mm幅のスリットを置いて、位置方向の観測軸を10ビットに拡げて測定を行なった。図5がそのデータである。有効桁は8ビットなので、若干システムティックなエラーが見える。

なぜ8ビットの有効桁か説明する。12ビットのQ1、Q2データから  $x/L = aQ2/(Q1+bQ2)-c$  を求める。割算を行なうため、分母になる  $Q1+bQ2$ (波高値)をあまり小さくできない。そこで、最大値の4分の1以下を捨てているので、最悪でも10ビットの精度が得られる(最大値で、12ビットの情報なので、4分の1付近では10ビットの情報しか得られないため)。さらに、PSDの不感帯を避けるために、aの値を1.5~3にとるので、3分の1程度に精度が落ち、8ビット程度になる。

写真2 SIRIUSグループに248本増設

図 5 右の、真中のピークの拡大図を見ると、半値幅が 6.75 チャンネルである。この時の、両サイドのピークの間隔は 577 チャンネルで、400mm であるので、半値幅は 4.68mm 相当である。2mm 幅スリット分を引くと 4.2mm の半値幅であることが求められた。

文献(1)では、さらに 3.8mm の位置分解能が得られている。

## 5 . PSD2K の使用状況

### 5.1 PSD の位置調整

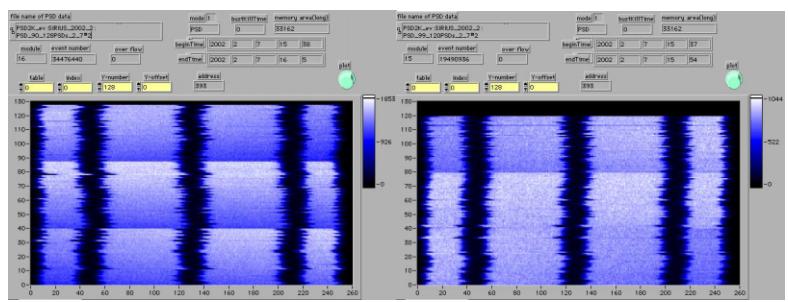

写真 2 に示すように、SIRIUS グループに 248 本の PSD を増設し、PSD2K システムで測定を開始した。測定する試料位置から 90 度方向に、左右 2ヶ所のバンク内に設置した。写真では右側だけが見えている。右側に 120 本、左側に 128 本を設置した。

図 6 に左側 128 本と右側 120 本の位置データを示す。横軸が PSD の位置で、縦軸が PSD である。調整のため、中心と、中心から 20cm 離れた位置に 4cm 幅のカドミウム板を 3 枚置いた。調整をしていない状態であるが、おおよそ合っているのがわかる。

図 7 に調整後のデータを示す。非常に良く合わせられたのがわかる。248 本の PSD 数時間で調整できた。

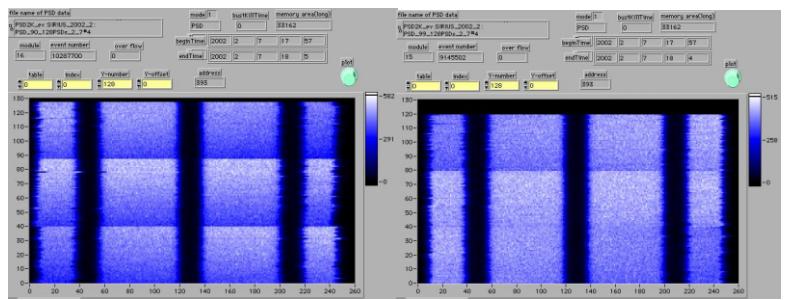

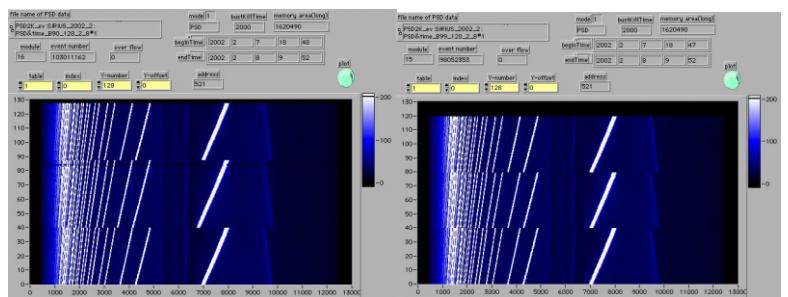

### 5.2 時間分析データ

図 8 にダイヤモンド粉末の時間分析データを示す。横軸がパルス中性子発生直後からの経過時刻（時間）で、縦軸が PSD である。試料のダイヤモンド粉末からの距離の差がピーク位置のずれでわかる。ここでは単純化のために、PSD の位置情報は使っていない。

### 5.3 時間補正分析データ

図 9 に有機物 thioamide の時間補正分析データを示す。横軸が時間で、縦軸が PSD である。図 8 を使用して、試料からの距離の時間差を補正し、ピーク位置がずれないようにした。

図 10 は図 9 のデータを足し合せたものである。このことから、少ない試料のデータを広面積で検出し、

図 6 248 本 PSD の調整前データ、横：位置、縦：PSD

左側：左 90 度バンク：128 本 PSD、

右側：右 90 度バンク：120 本 PSD

図 7 248 本 PSD の調整後データ

図 8 ダイヤモンド粉末のデータ、横：時間、縦：PSD

図 9 有機物 thioamide のデータ、横：時間、縦：PSD

図 10 有機物 thioamide のデータ、横：時間、縦：カウント数

補正して足し合わせ、効率が上げられるのがわかる。

## 6 . PSD 支持箱

### 6.1 PSD 支持箱

PSD 支持箱の基本設計は、第二世代から変わっていない。2枚の検出器基板からなる。写真1のように、前面に8本の検出器が隙間なく配置でき、その裏側にアンプが収納できるようにしている。

### 6.2 検出器基板

検出器基板は9枚のAMP97カードから構成される。この中の1枚のカードはシールドと予備用で、8枚が動作する。

検出器基板は電源供給・信号分配ラインと、テスト回路を持つだけである。1枚の検出器基板と8枚のAMP97カードの消費電流は、+12Vで136mA、-12Vで-108mAの実測値であった。したがって、1台のPSD支持箱では、+12Vで272mA、-12Vで-216mAとなる。20スロットのVME電源を使用した場合、最大で19台のPSD支持箱が使用されるので、必要な電源は、+12Vで5.2A、-12Vで-4.1Aとなる。このため、汎用品のVME電源が使用できる。

### 6.3 AMP97カード

AMP97カードは、電荷感応型のプリアンプと波形整形回路（アクティブフィルタ）で構成される。

表面実装部品で構成し、裏面の全てをアース面にし、シールドを強化した。並べて配置して、お互いのアース面でシールドし、クロストークが小さくなるようにした。また、調整箇所を無くした。ポールゼロ調整は最適値の固定抵抗で十分に合うことが確認されたので、省略した。DCレベル調整もデジタル処理で自動的に合わせられるので、省略した。

## 7 . PSD2Kモジュール

### 7.1 P12virカード

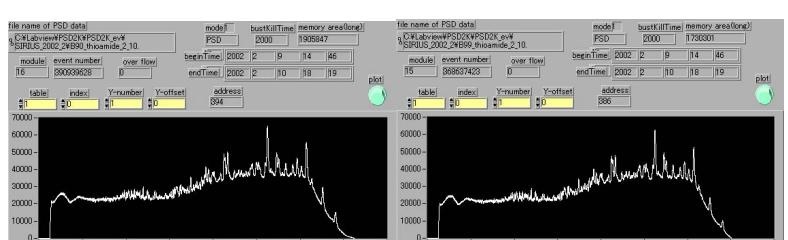

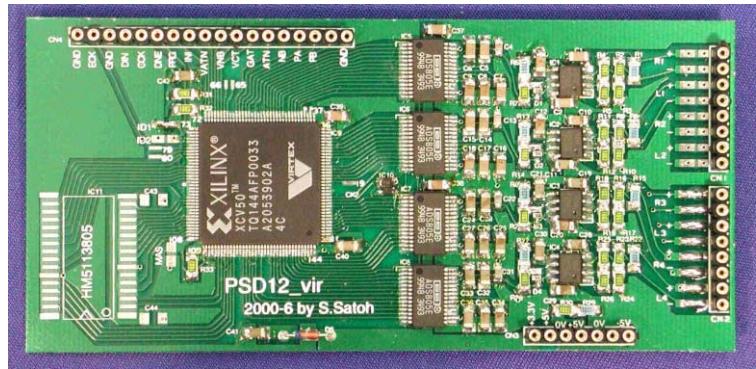

PSD支持箱からのパルス信号を、高速なADCを使用し、12bit精度、20MHzのサンプリングレートでデジタル化する。図2の真中、上に相当し、P12virカード1枚は、これを2回路持ち、2本のPSDが処理できる。

写真3にP12virカードを示す。表面実装部品で構成し、裏面をできるだけアース面にした。ドーターカードとして、重ねて使用する。

信号の波高値は、单一波形の最大値から

写真3 P12virカード

最小値を引いて求める。これを視覚的に表したのが図11である。

パルス波形の検出は、クロック(CLK: 20MHz、50n秒周期)ごとに前のデータと比較し、連続して8クロック分(400n秒)大きくなった時に、パルスの立ち上がりとみなす。この状態以降で、前のデータより小さくなった時点をピークと判断し、この間の最大値を保存しておく。

最小値は、ピーク検出時間から32クロックから48クロック(1.6~2.4μ秒)前のデータの、16クロック間(0.8μ秒)の最小値をとる。先ほどの最大値から、これを差し引いて、ピーク値とする。

PSD左右の、二つの信号のピーク検出時間が200n秒の間にあつたら、中性子データとみなして保存する。その後、PSD2K-VME基板からポーリングされたら、このデータを送る。PSD1本分のデータは、左右のピーク値24ビットと、時間情報16ビットである。

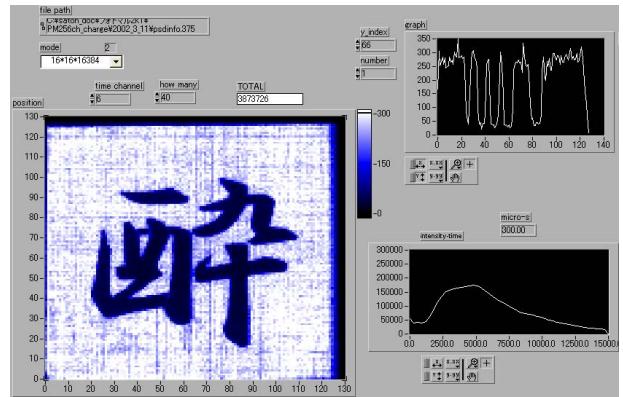

このカードは波形記録機能を持つ。PSDの左右からの二つの信号を同時に、12ビット、32サンプリング分の波形が記録できる。サンプリングのクロックも、20MHz、10MHz、5MHz、2.5MHzの中から選ぶことができる。これにより、各信号の健全性を目で確かめることができる。

図11 パルス波形からピーク値を求める方法

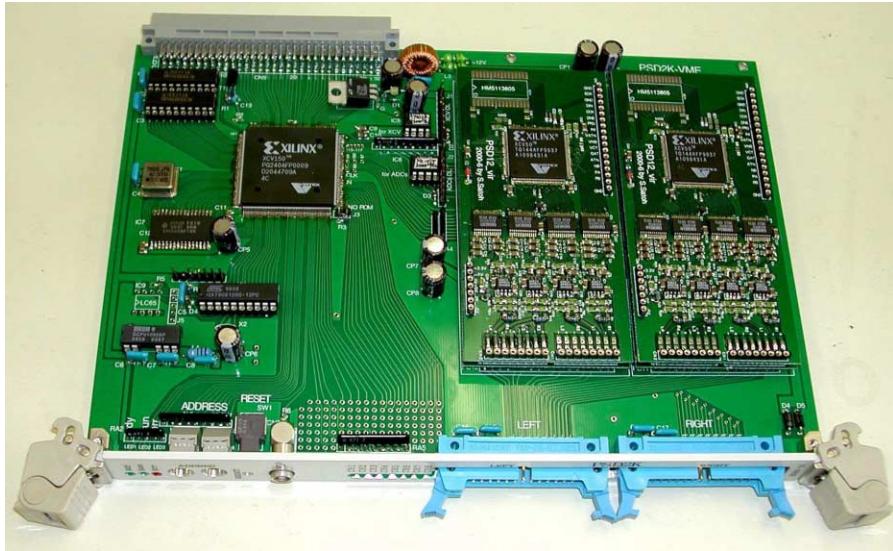

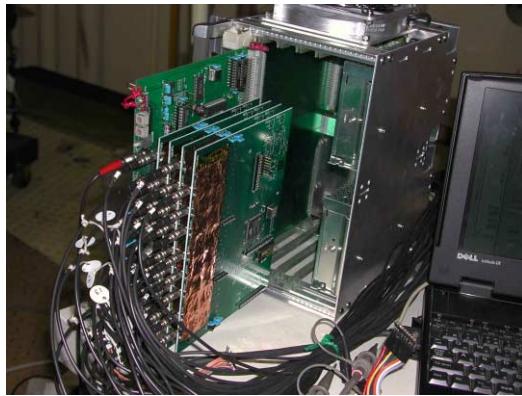

写真4 PSD2K-VME ボード

## 7.2 PSD2K-VME ボード

写真4に PSD2K-VME ボードの写真を示す。一枚幅のダブルハイット VME ボードで、8本の PSD のヒストグラムデータを蓄積、更新していく。ヒストグラム用メモリとして 16M バイトを持つ。

8本全てで、それぞれ 64 位置分解能で見た時、8K チャンネルの時間分解能で測定できる。データ幅はロングワード (4 バイト) である。この他に、128 位置分解能 - 4K 時間分解能、256 位置分解能 - 2K 時間分解能が選べる。

4枚の P12vir カードからのデータ読み出しは、4 本の共通ラインで、ポーリングによって行なう。読み出すデータは PSD の左右の波高値と時間情報である。この方法により、製作が容易になった。0.5 μ秒以内で読み出せるので、後に続く位置の計算も 0.5 μ秒で行ない、並列処理ができるようにした。

40MHz クロックで同期を取りながら、各 PSD をポーリングする。データがない場合は 4 クロック、ある場合は 20 クロックの時間が掛かる。8 本の PSD を検査するのに、最小で 32 クロック (0.8 μ秒)、最大で 160 クロック (4 μ秒) かかる。

並列処理を円滑に行なうために、左右の波高データ 24 ビット、時間情報 16 ビット、検出器番号 3 ビットの 43 ビットを、最大 16 セット記憶できる FIFO (先入先出し) バッファに、一時記憶する。

計算部分は、1 中性子当たり 18 クロックで計算する。基本的な関係式は  $x/L = Q2/(Q1+Q2)$  となり、 $L$  が PSD の全長、 $x$  が中性子が当たった場所までの距離、 $Q1$  と  $Q2$  が PSD の両端に出てくる電荷である。これに微調整のための、倍率(a)、比率(b)、オフセット(c)を含め、 $a*Q2/(Q1+b*Q2)-c$  の計算をする。

計算は 2 段の並列処理で、初段と後段に分けられる。初段で  $A=a*Q2$  と  $B=(Q1+b*Q2)$  を並列に求める。初段の結果で、波高値の合計  $B$  が敷居値(d)を超えて

いなければ、捨てる。そして、後段で位置を求める除算とオフセットの引き算、A/B-c を行ない、位置情報とする。乗算はクロックごとにシフトさせ、ビットが立つていれば加算する、アキュームレート法を使用する。除算はクロックごとにシフトさせ、除数を引き、ポートが出たら除数を戻す、引き戻し法を使用する。a と b を固定小数点として扱う。

初段、後段とも、同じ 17 クロックで処理する。結果は波高値の合計 12 ビット、位置情報 10 ビット、時間情報 16 ビット、検出器番号 3 ビットの 41 ビットを、最大 16 セット記憶できる FIFO

バッファに、一時記憶する。

最後にヒストグラムを更新する。2001 年 7 月現在で、ヒストグラムは 4 種類ある。一つは 1024 位置分解能と 256 波高分解能の、2 つのヒストグラムを作るモード 0 である。位置合わせなどに使用する。残りの 3 種類は位置分解能と時間分解能の組み合わせで、64 - 8192、128 - 4096、256 - 2048 の、モード 1 ~ 3 がある。データの大きさを変えやすいように、読み出しの配列の次元を (時間、位置) としている。位置情報が先に読み出せるので、時間分解能が少ししか要らない時、必要な時間分だけ読み出し、データを小さくできる。

メモリのデータバス幅は 8 ビットで、データの更新には 1 バイトで約 100n 秒かかる。モード 0 では、1 中性子当たり、ヒストグラムを 2 個更新するので、200n 秒かかる。

さらに桁上がりで更新回数が増える。カウント数が 256 の時 2 倍、65,536 の時 3 倍、16,777,216 の時 4 倍に伸びる。したがって最悪で 800n 秒かかるが、16,777,216 回に 1 回と、非常に頻度が小さいので、前段の FIFO バッファで吸収され、8 本の PSD 分が一度に来ても 1.6 μ秒程度で処理できる。モード 1 ~ 3 では、1 中性子当たり、ヒストグラムを 1 個更新するだけなので、モード 0 より半分の時間で済む。

計算係数の倍率、オフセット、比率、敷居値を EEPROM に記憶させている。それぞれの値は 16 ビット長で、4 種類あり、PSD 1 本につき、8 バイト必要である。値をセットする PSD を、VME アドレス 5 の 2 ~ 0 ビットで指定する。それぞれの値のセットは VME アドレス 8 ~ 15 の、8 バイトの空間を使用する。

8 本の PSD のデータには、64 バイトの EEPROM が必要である。測定停止中にステータス (アドレス 5) に、0x40 を書き込むことによって、EEPROM へ自動的に書き込まれる。また、0x60 を書き込むこと

によって、EEPROM から自動的に読み取られる。電源投入時にも読み取られ、自動的に設定される。

パルス中性子実験では時間分析機能が重要であるので、パルス中性子発生直後（キッカーパルスで知らされる）からの時刻を知らせる信号（時間チャンネル）を発生し、中性子を捕獲した時刻の記録に使う。また、測定遅延時間は、パルス中性子発生直後のバーストをカットするもので、128  $\mu$ 秒単位で0から1023まで設定できる。

時間チャンネルはフラットモードと  $dt/T = \text{一定}$  モードがある。フラットモードの場合は単位が1  $\mu$ 秒となり、0から1023まで設定できる。設定した値で、一定の間隔の時間チャンネルとなる。

$dt/T = \text{一定}$  モードの場合はキッカーパルスからの経過時間に比例した時間チャンネルが与えられる。4種類の設定があり、128  $\mu$ 秒ごとに125、250、500、または1000n秒づつ増えていく。

測定遅延時間は、キッカーパルスから遅延時間後に測定が開始されるようにする。特に、 $dt/T = \text{一定}$  モードで、キッカーパルスからの経過時間を使用するので、128  $\mu$ 秒ごとにカウントアップする10ビットのTM[9:0]を出力する。遅延時間が経過していない間は、キッカーパルスが来ても無視し、前の測定を続ける。冷中性子実験で必要な機能である。

データの高速転送ができるように、書き込み、読み取り用に FIFO バッファを持つ。それぞれに32バイトの容量を持ち、待ち時間を最小限にした。

最高速度で、VME からの書き込みに250n秒/16ビット、読み出しに200n秒/16ビットで対応できる。測定中の読み出しでは、これにヒストグラムの更新のメモリアクセスが加わるので、少し遅くなる。しかし、十分に空き時間があるので、最大でも2~3割程度の遅れにしかならない。

SCSI-VME\_2K モジュールを同時に開発し、これらの機能が有効に働くようにした。従来の SCSI-VME モジュールでは 1M バイト/秒程度の転送速度しかないので、16M バイトの読み出しに、16秒もかかってしまう。SCSI-VME\_2K モジュールの開発と PSD2K モジュールの改良を行ない、8M バイト/秒が実現でき、2秒で読み出せる。コンピュータにマッキントッシュの G4 と、ウルトラ SCSI の PCI ボード（8ビット幅、ロジテック LHA-600 シリーズ、4千円弱）を使用した。

VME 側の待ち時間が最小の場合、10M バイト/秒の転送速度が得られるのがわかる。使用している DRAM メモリ（16M バイト）は、もっと高速読み出しが可能なはずなので、アクセス方式を工夫すれば、さらに高速化が期待できる。

## 8. 高速転送 SCSI-VME\_2K モジュール

前述のように、今までのものは 1M バイト/秒程度であったので、高速転送できる SCSI-VME モジュールの開発を行なった。使用する SCSI をウルトラ

SCSI とすると、20M バイト/秒程度まで高速化が可能である。

PSD2K モジュールと同じ基板を使用し、ワンチップマイクロコンピュータ（マイコン）を載せた増設基板を加えた。SCSI の制御のほとんど全部をマイコンで処理し、データフェーズだけをゲートアレイで行なう。ゲートアレイは SCSI のコマンドフェーズ、メッセージフェーズを傍受し、同期転送モードの有無、REQ/ACK オフセット値、最小転送周期、VME アドレス、データ転送数などを自動的に取り込み、データフェーズの時に使用する。

ゲートアレイでのデータ転送は、VME バスのアービトレーションから始まる。SCSI 側で、すでに同期転送モードが指定されていれば、REQ/ACK オフセット値に沿い、ATN 信号が返らなくても REQ 信号を先行し、データ転送を行なう。

VME のデータ転送では、コントローラが DS0,1 信号をローにした瞬間に、DTACK 信号をローにして返すモジュールが一番速い。そこで、DS0,1 信号を DTACK 信号として返すテストモジュールを使用すると、12M バイト/秒程度の高速転送が確認できた。また、非同期転送モードでも、4.5M バイト/秒程度の転送ができた。

高速化の秘密は FIFO バッファを持たせ、パイプライン処理（並列処理）を多くしたことである。こうすることにより、待ち時間が減り、高速化ができた。

## 9. 他のシステムへの応用

### 9.1 2次元検出器、Bidim80

この PSD2K システムは、プログラマブルゲートアレイで設計しているので、他のシステムへの応用が容易である。

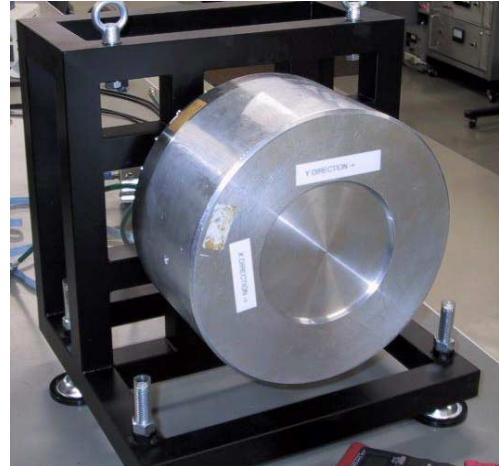

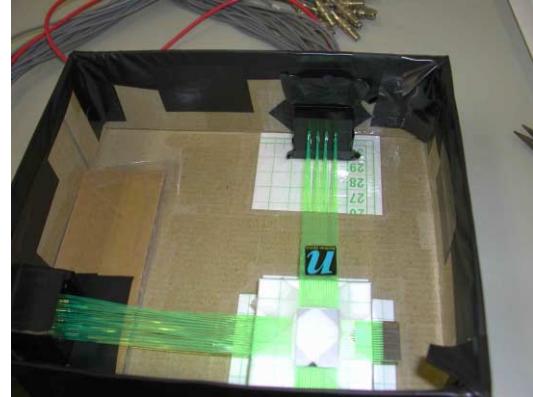

写真 5 2次元検出器、Bidim80

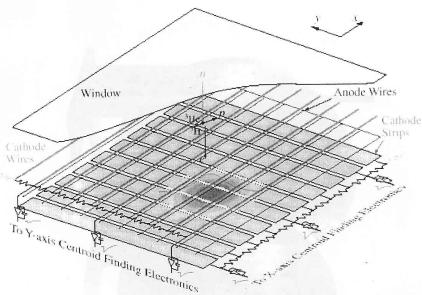

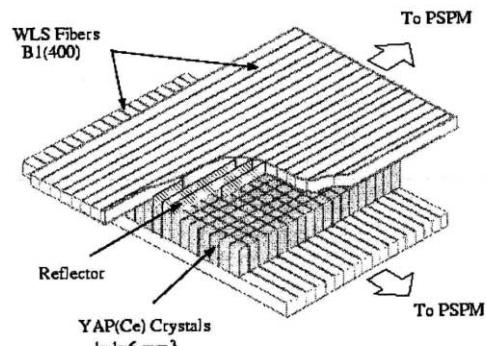

写真 5 にフランスの ILL 研究所で開発された2次元検出器 Bidim80 を示す。He-3 ガスを封入した、2次元のマイクロストリップ検出器である。図 12 にその原理図を示す。基板の両面にマイクロストリップを直交するように配置し、中性子が He-3 ガスに捕

獲されて発生する電荷を両面で検出する。検出された電荷はそれぞれのマイクロストリップを伝わり、抵抗分割法で処理される。

図 1.2 マイクロストリップ検出器の原理図

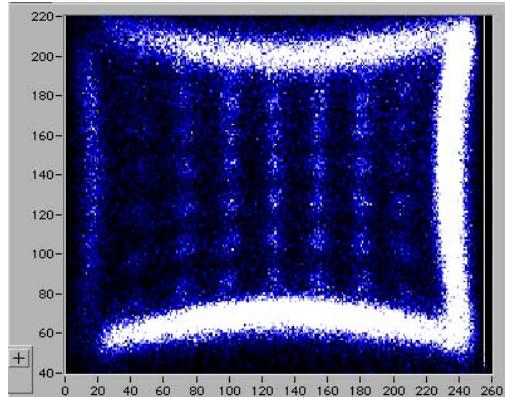

図 1.3 に、この 2 次元検出器の出力を解析したデータを示す。ILL 研究所は原子炉で中性子を発生させているため、時間分析機能がないが、パルス中性子源では絶対に必要である。このデータは北海道大学でのパルス中性子源で、縦横 8cm\*8cm の検出エリア内に、1cm 間隔ごとに 1mm 平方の穴を開けたカドミストリットを置いた結果である。パルス中性子発生後、2 ミリ秒経過から 250  $\mu$  秒間のデータである。横方向が約 2mm、縦方向が約 3mm の分解能であった。歪みが見えるので、なんらかの補正が必要と思われる。

図 1.3 2 次元検出器データ

この ILL 研究所で開発された 2 次元検出器は、4 つの信号を出力し、2 次元の位置を表わす。2 信号で X 軸の位置を、残りの 2 信号で直交する Y 軸の位置を表している。この 4 信号を観察した結果、完全に同時になく、600n 秒程度の間に到着する。これを踏まえて、次のような変更を行なった。

1 - PSD2K モジュールは 16 信号から、8 本の PSD のデータ処理を行なっているが、この内、2 本分の処理機能だけを使用した。1 本目を X 軸、2 本目を Y 軸とした。

2 - X 軸、Y 軸共にフルスケールの解析を許すために、左右の信号のどちらか片方の入力だけでも中性子検出とする。ただし、800n 秒の間は待つ。さらに 800n 秒の間に、X 軸と Y 軸の両方に来なければならぬ。

3 - 位置と時間軸で測定する場合、X 軸、Y 軸、時間軸の順に、255\*255\*64、128\*128\*256、64\*64\*1024 の大きさとなる。

## 9.2 ファイバー 2 次元検出器（パルス式）

理化学研究所が作製した、X 軸に 16 本、Y 軸に 16 本のファイバー 2 次元検出器用の読み出し回路を作製した。写真 6 に構成を、図 1.4 に原理図を示す。写真右下の ZnS シンチレータの両面に、直交させた 1mm 角の光ファイバーを取り付け、2 本の 16 チャンネルのマルチフォトマルで受けている。

写真 6 16ch\*16ch ファイバー検出器

この検出器の読み出し回路に PSD2K モジュールを応用している。ファイバーで送られた光をマルチフォトマルで検出し、この読み出し回路で位置を求める。

図 1.4 ファイバー検出器の原理図

写真 7 に読み出し回路を示す。PSD2K モジュールを母体とし、32 チャンネルの信号を処理するボードを 4 枚取り付けている。

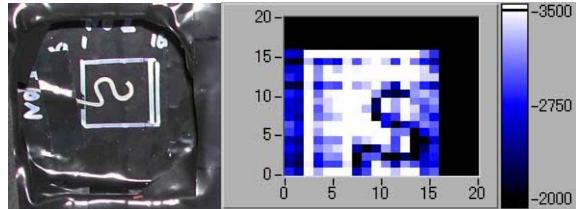

フォトマルから出力される高速パルス（半値幅 4ns 弱）をカウントする方式で中性子を識別した。写真 8 に検出面に貼りつけたカドミウムのマークを、図 1.5 に読み出し回路のデータを示す。He-3 ガス検出器に比べ、10 ~ 20% の検出効率であった。

写真 7 パルス式 2 次元読み出し回路

写真 8、図 15 カドミウムのマークと、読み出し結果

### 9.3 ファイバー 2 次元検出器（チャージ式）

ILL 研究所が作製した、X 軸に 128 本、Y 軸に 128 本のファイバー 2 次元検出器用の読み出し回路を作製した。原理は 9.2 と同じで、図 14 のようになる。検出部分の構成は ZnS シンチレータの両面に、直交させた 0.4mm 角の光ファイバーを取り付け、4 本の 64 チャンネル・マルチフォトマルで受けている。

写真 9 にチャージ式 2 次元読み出し回路を示す。17 台の PSD2K モジュールを使用して読み出し、データ処理を行なう。

フォトマル出力をチャージアンプで受け、PSD2K システムと同様に、ADC で波高値を求める。X 軸と Y 軸でコインシデンスを取り、各軸の最大値の位置を中性子捕獲位置とする。

写真 9 チャージ式 2 次元読み出し回路

写真 10 に検出面に貼りつけたカドミウムのマークを、図 16 に読み出し回路のデータを示す。非常

に良いデータが得られるのがわかった。He-3 ガス検出器に比べ、10 ~ 20% の検出効率であった。

写真 10 カドミウムのマーク

図 16 読み出し結果

## 10 . PSD システムのための検査回路

### 10.1 PSD 検査回路

PSD 検査回路は PSD システムの健全性を簡易に検査するためのものである。基本的な構成は、制御用のワンチップマイコンと、2 個の 12 ビットの D/A 変換器である。検査方法としては 2 種類の方式に分かれる。一つは実際の PSD を正確に真似て測定する、抵抗方式である。もう一つは、PSD システムに組み込んであるテスト回路を使用して、使用中の PSD システムの健全性を常に検査できる、テスト回路方式である。

写真 11 に抵抗方式の位置分解能検査回路の、一般的な使用例を示す。抵抗方式は PSD に真似た抵抗アレーの 8 箇所に、1pF のコンデンサを介してパルスを加える。このパルスは、一方の D/A 変換器からの出力で作る、振幅が変わる矩形波であり、同時に 2 箇所以上に加えない。この写真の例では、4 枚の PSD 検査回路を使用し、PSD 4 本分のテストを一度に行なうものである。

任意の 1 箇所にパルスを加えると、実際の PSD と同じに、抵抗分割された電荷が左右の両端に出力される。実際に使用されるチャージアンプで受けるこ

とにより、忠実にシステム全体の位置分解能の測定ができる。写真11では、アルミケースに入れた、AMP97カードを載せた検出器基板(アンプボックス)を使用している。この信号を文献(2)に載せたPSDコネクタ基板で左右の信号に振り分け、PSD2Kモジュールに入力し、健全性、処理精度等を確認する。

写真11 抵抗方式の位置分解能検査回路

## 10.2 時間機能検査回路

時間機能検査回路は写真12のような回路で、時間制御回路と、パルス発生回路と、カウンタで構成されている。時間制御回路はプログラマブルゲートアレイ1個で構成され、パルス発生回路と、カウンタは別クロックで動作し、それぞれが独立している。

時間制御回路は、20Hzの基準周波数を発生させ、これから設定した時間遅らせ(遅延時間)、設定した時間ゲートを開いて(ゲート時間)、この間だけパルスを出力する。そして、通過するパルスの総数を設定できる(総パルス数)。

パルス発生回路は、ゲートを通過するパルスを発生させ、その周波数の設定ができる。カウンタは、ゲートを通過するパルスを独立にカウントすることにより、時間制御回路が正しく動作しているのを確認できる。

写真12 時間機能検査回路

この検査回路は、文献(2)などにも紹介している、TA17XC等の時間分析器の検査用に開発した。TA17XCに、アンプボックスの替わりに取り付け、電源はフラットケーブルから供給される。8入力同時に検査ができる。

PSD2Kシステムでの使用方法としては、写真11のアンプボックスの8入力全部に1pFのコンデンサを通して接続する。検査回路に4個の設定スイッチがあるが、例として左から2, 7, 7, 4と設定する。この場合、周波数100kHz、遅延10ミリ秒、ゲート10ミリ秒、総パルス100000カウントが設定されたことになる。

PSD2Kシステムを測定準備し、カウントをスタートさせると、"TOTAL"のカウント表示が"100000"で止まるのが確認できるはずである。この時の検査回路の表示も"100000"であれば、PSD2Kモジュールが取りこぼさなかったのが確認される。この状態で、時間軸で10000μ秒からデータがあり、20000μ秒で無くなっているのを確認する。このようにして、時間機能の検査を行なう。

## おわりに

長年、中性子検出器システムの開発をしてきたが、PSD2Kシステムは集大成といえる。これで技術賞が取れ、感無量の思いがある。今後も、さらに高性能のシステムを目指したい。

システムのデジタル化は、時代の流れである。アナログ部品そのものが消えかかっている。アナログ方式からデジタル方式に変える最適な条件が揃っていて、PSD2Kシステムの開発は必然であったと思う。

PSD2Kモジュールはプログラマブルゲートアレイの比率が大きいので、非常に自由度がある。ゲートアレイのプログラムは簡単ではないが、ハードウェアの変更なしに他のシステムに応用できるのが実感できた。

現在は、最後の方に紹介した、ファイバー2次元検出器の読み出し回路の開発に力を注いでいる。各方面からの要望も多く、新しい中性子検出器システムとして期待されている。

## 参考文献

- [1] 佐藤節夫他. "中性子散乱実験用位置敏感検出器、PSD2Kシステムの開発", KEK Report 2001-9 August 2001 M/D

- [2] 佐藤節夫他. "中性子散乱実験用データ収集用装置の開発", KEK Internal 96-14 November 1996 M

- [3] 佐藤節夫他. "PSD(Position Sensitive Detector)システムの開発", KEK Internal 93-10 November 1993 M/D

- [4] 佐藤節夫他. "8入力小型アンプ及び多入力時間分析器の開発", KEK Internal 92-4 April 1992 M/D

- [5] グレン F.ノル. "放射線計測ハンドブック", 日刊工業新聞社 1996年10月25日第2版2刷、ISBN4-526-02873-8 C3050

- [6] "SCSI完璧リファレンス", OPEN DESIGN NO.1, 1994年3月1日、CQ出版社

- [7] 佐藤節夫. "SCSI-ビデオ信号ボードの製作", トランジスタ技術、2000年1月号、pp.339-350、CQ出版社

- [8] 佐藤節夫. "SX18/20/28シリーズの概要と評価", トランジスタ技術、1998年12月号、pp.284-297、CQ出版社