新たな現象や非常に稀な現象を捉えることを目標とする世界最先端の研究において、センサーや信号処理システム等の装置は世界に 1 つしか無いため自分自身で開発しなくてはなりません。エレクトロニクスシステムグループ(E-sys)では、このような世界に 1 点だけの実験装置のセンサーからシステムに至るまでを各実験グループと連携して開発し、それらを Open-It を通して知と技術の共有を行っています。これらの活動は測定器開発センター(ITDC)の一員として行なっています。

E-sys は、つくばキャンパス(E-sys つくば)と東海キャンパス(E-sys 東海)の2カ所の研究開発教育拠点からなります。E-sys つくばは半導体検出器および信号処理用エレクトロニクスの要素開発(集積回路開発、PCB:Printed Circuit Board 開発)に関し E-sys 東海と連携し研究開発を推進しています。

# 1. プロジェクトへの貢献

### ● E-sys つくば

つくばサイトでは、EF グループ、Belle II グループ等コライダー実験を行うグループとの連携開発だけでなく J-PARC における実験用測定装置開発も推進しています。 つくばサイトでは要素技術開発が主ですが、E-sys 東海と協力してシステム開発も行なっています。

#### (Belle II CDC 読出し用エレクトロニクス開発)

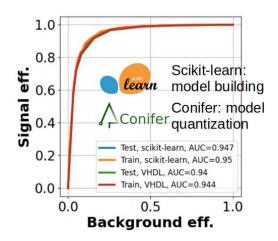

Belle II 検出器の Central Drift Chamber(CDC)読出しボードである RECBE(図1(a))では、クロストークノイズ(ほぼすべてのチャネルで同時に信号が生成される現象)が問題となっています。私たちは、フロントエンドエレクトロニクス(FEE)の ADC 波形を用いてノイズを識別するための機械学習ベースのファームウェアモジュールを開発しています。 トリガーシステムとは異なり、FEE に搭載されている FPGA(Xilinx 社製 Virtex-5)は小型であるため、チャネルごとの並列処理を行うには、機械学習モデルを非常にコンパクトにする必要があります。そこで、Boosted Decision Tree(BDT)を用いてモデルを構築しました。 FPGA への実装は自作の VHDL モジュールで行っており、 Virtex-5 FPGA のリソース使用率は 5%以内、レイテンシもわずか 2 クロックサイクルと非常に効率的です。また、ハードウェア実装前後で Area Under Curve(AUC,1 に近いほど良い)の劣化が生じないことが確認できました(図 1(b))。

なお、この研究は、Collider Electronics Forum(CEF)の新設タスクフォース「AI in FEE」の一環 として進められており、素粒子検出器の FEE における AI 応用と実装に向けて、コンパクトなモデルの開 発を中心に取り組んでいます。素粒子物理以外のフロントエンドレベルでの応用も期待されています。

#### (モノリシックピクセルセンサー開発)

Belle II アップグレードのためのモノリシックピクセルセンサーの開発に携わっており、ストラスブール大学を中心とした国際共同開発グループの一員として OBELIX-1 チップの開発を行っています。特にチップの安定動作に欠くことのできない重要な回路ブロックである電源回路の設計を中心に貢献しており、様々な動作条件における安定性の解析を中心に検証を進めています。

### (COMET 実験に向けたエレクトロニクス開発)

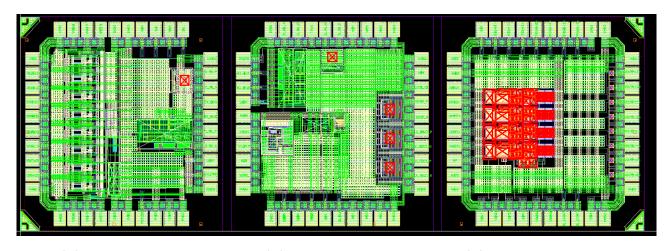

COMET Phase-1 実験に向けて、SiC をセンサとして用いたミューオンビームモニタの開発に携わっており、SiC からの信号を読み出すための SCIBER と呼ばれる ASIC の開発を進めています。SCIBER は昨年度までに2回の試作を行っていますが、これまでに判明した課題を解決するために機能を個別のチップに分けた SCIBER3 の試作を行いました。SCIBER3 (図2)は3つの回路ブロックから構成され、SiC からの微弱な信号ぞ増幅するためのアナログフロントエンド(SCIBER3 AFE)、アナログ信号をデジタル信号に変換し、十数メートルの距離を 640Mbps で伝送する ADC チップ(SCIBER3 ADC)、ADC から高速に送られるデジタルデータを受信するためのチップ(SCIBER3 RX)があります。2025年 6 月に65nm CMOS プロセスを用いてテープアウトを行い、現在はチップの実装、評価基板および環境の整備を行っているところで、今年度内には ASIC 群の評価を終える予定です。

|                      | LUT  | FF   | Latency                 |

|----------------------|------|------|-------------------------|

|                      | 4386 | 2640 | 2 clock-cycles<br>15 ns |

| Fraction in Virtex-5 | 4.5% | 2.7% | -                       |

(a) RECBE ボード

(b) FPGA 使用率と ROC 曲線

図1 RECBE のクロストークノイズを低減するための機械学習モデルの実装

(a) SCIBER3\_ADC

(b) SCIBER3\_RX

(c)SCIBER3\_AFE

図2 COMET実験用ミューオンビームモニタ信号読出しASIC(SCIBER3)

## ● E-sys 東海

東海サイトでは主に J-PARC:現場で開発や改良が必要であることが多いデジタル技術を中心として研究開発を行いつつ、J-PARC センター利用者が専門家と連携し研究開発を進めるため、共同利用実験室を設置し開発に必要な測定器などの機材も用意しており、毎日大学院生・若手研究者が利用しています。技術特徴は ASIC、FPGA に搭載するデジタル回路開発、10Gbps を超える高速転送技術、データ収集システムの構築やデータ収集用プラットフォーム開発です。

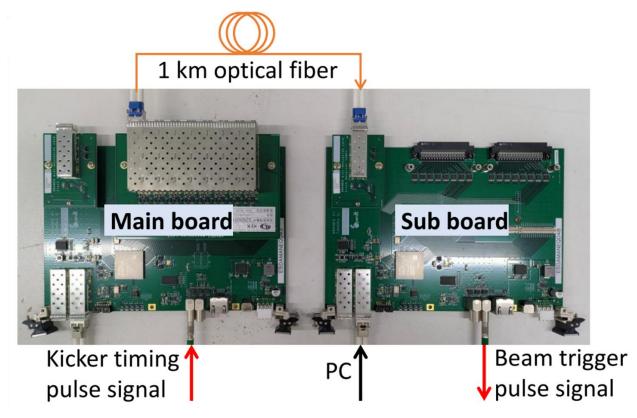

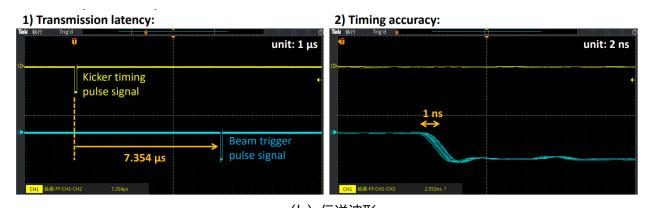

#### (T2K/Hyper-K 実験用のトリガー伝送システムの開発)

T2K 実験ではトリガー信号を J-PARC 内のニュートリノ諸施設に伝送するために、光ファイバーによるシステムを用いています。このシステムは K2K 時代に作られたもので、老朽化により設備更新が急務です。また、Hyper-K 実験では中間検出器(IWCD)を J-PARC 外へ設置するため、IWCD へも同様にトリガー情報の伝送が必要になり、最大 10 kmの光ファイバーで通信を行う必要があります。この課題を解決するため、ITDC E-sys 東海分室が開発した MIKUMARI link protocol をベースにしたトリガータイミングおよびスピル番号を長距離伝送するシステムの開発を行っています(図 3 (a))。このシステムはトリガータイミングとスピル番号をデジタルデータとして遠方に送信し、1ns 精度でトリガータイミングを再現することが出来ます。これまで 1 kmのファイバーで試験を行い上記性能が達成できることを確認し(図 3(b))、得られたエラー発生率(トリガーロスト)の上限値は < 4.6x10^-11 (95% C.L.) でした。これは 10 年間運転を行った場合でも、トリガーロストが発生する可能性が 1.1%程度であることを示し、高い安定度を誇ります。今後は 10 km通信に必要な技術の開発を進める予定です。

### (MTM-MIKUMARI 同期システム)

ITDC E-sys 東海分室では連続読み出しDAQ システムの開発を推進していますが、連続読み出し型のDAQ とトリガー型のDAQ を同時に使用したいという場面が存在します。そのような場合に、トリガー型DAQが持つトリガー番号などのイベント情報と、連続読み出しDAQが時刻ドメインを結合して、両者のデータ接続を安全に行うための回路が必要です。本グループでは J-PARC 実験で使われている Master Trigger Module (MTM) が生成するトリガー信号のタイミングとイベント番号を、MIKUMARI システムが定義する時刻と結合する FPGA ファームウェア、Streaming Receiver Module (Str-RM)を開発して AMANEQ 回路基板へ実装しました。今後、様々利用シーンにおいてトリガー型DAQ との接続に使用できるよう展開に努めます。

## (DAQ-middleware の最終リリース)

DAQ-Middleware はネットワーク分散環境でデータ収集用ソフトウェアを容易に構築するためのソフトウェア・フレームワークです。国際標準ロボット技術であるロボットテクノロジーミドルウエア(RT-Middleware)の実装 OpenRTM-aist をベースにしており、2006 年、当時の KEK 測定器開発室次世代 DAQ プロジェクトとして開発が始まりました。以来、ソースコードの他に Scientific Linux、CentOS の各バージョンに対応した RPM パッケージも提供しておりました。2025 年に OpenRTM-aist 最新版をもとにした AlmaLinux 9 対応版をリリースしました。これまで素粒子原子核実験の様々シーンおいて、DAQ-middleware は活用されてきましたが、この対応版が DAQ-Middleware の最終リリースとなります。今後は、次期 DAQ ソフトウェアとして NestDAQ への移行を推進していきます。

(a) MIKUMARI link protocol による伝送テストボード

(b) 伝送波形 図 3 T2K/Hyper-K 実験用のトリガー伝送システム

# 2. 萌芽研究•技術開発

● MIKUMARI による時刻同期ファミリの拡大

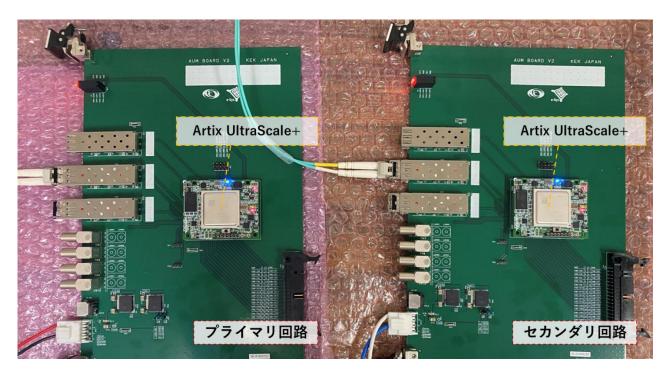

本グループが開発している MIKUMARI link protocl と時刻同期プロトコル(LACCP)はこれまで AMD Xilinx の 7 シリーズのみでしか使用できませんでした。DAQ システムでは様々な FPGA デバイス が回路基板に使われることから、使用可能なデバイスファミリを拡大することが肝要です。そこで、AMD Xilinx の主要デバイスである UltraScale ファミリへの拡張を行いました(図4)。時刻同期プロトコルでは合わせたいデバイスと基準となるデバイスとの間で信号をやり取りし、その往復時間を測定することで時刻オフセットを得るというのが基本的な戦略です。LACCP は 300ps 確度での時刻同期を行うプロトコルですから、往復時間は 100ps 程度の精度で測定しなければなりません。この時、お互いのデバイスが同一であれば往路と復路にかかる信号の伝送遅延のうち、様々な固有遅延がキャンセルしてオフセット推定が簡単になりますが、異なったデバイス同士ではキャンセルしないためこれまで無視していたデバイス固有の遅延量を正確に求める必要があります。これらを自動で測定できるように改良し、異なったデバイス間でも同様の性能で時刻同期が出来るように改良しました。今後、様々なフロントエンド回路へ実装される予定です。

図4 MIKUMARI link protocl と LACCP の UltraScale ファミリでの動作試験

# 3. コミュニティ・教育活動

我々は複数の機関と連携し、エキスパートとのコラボレーションネットワーク Open-It、コライダーエレクトロニクスフォーラム(CEF)、SPADI Alliance(SPADI-A)を通して教育活動、プロジェクト推進を通したコミュニティ全体への積極的な寄与を行っています。

Open-It は「教育」と「連携」をキーワードにした、1)教育プログラム、2)連携開発プログラム、3)交流プログラムの 3 つを中心に活動しています。(https://openit.kek.jp/)

CEF では、タスクフォースとして、コライダー実験用高性能 FPGA と AI 技術を用いた高機能高速トリガー生成技術開発と 40Gbps を超える高速転送技術の開発を推進するために、ATLAS、Belle II、ALICE 及び関係大学と連携して活動を行っています。(https://kds.kek.jp/category/2369/)

SPADI-Alliance (SPADI-A)は DAQ システムの共通化・標準化を掲げ原子核分野を中心として立ち上がったアライアンスであり、E-sys はその運営において、阪大 RCNP データ収集基盤室、理研 RNC 情報処理チーム、東大 CNS、東北大 ELPH とともに中核を担っており、7 つのワーキンググループ(WG)を設置して、それぞれの目的とする開発研究を行っています。 (https://www.rcnp.osaka-u.ac.jp/~spadi/)

今年度の具体的な活動は以下の通りで、Open-It のセミナーシリーズを多数開催し、DAQ システムの開発の基礎の普及に努めました。

## CEF、Versal タスクフォース

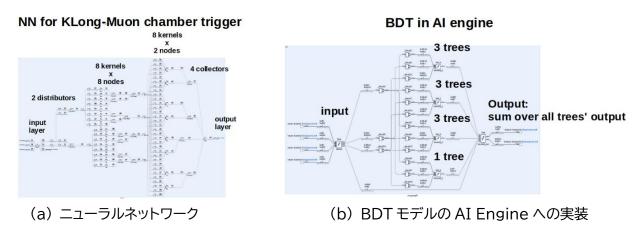

このタスクフォースでは、Xilinx 社の Versal ACAP を中心に、素粒子実験の DAQ システムへの応用を目指して研究を進めています。Versal は大規模なプログラマブルロジックに加え、計算加速エンジン (AI Engine や DPU)を搭載しており、トリガー用の高速アルゴリズム開発に非常に適しています。

私たちは、Belle II のトリガーアルゴリズムを基に、ニューラルネットワークや BDT モデルを Versal の AI Engine に実装しました。さらに、特定のアルゴリズム開発にとどまらず、さまざまな開発・実装技術を 体系化し、技術データベースを構築しました。このデータベースには、高位合成、機械学習(ニューラルネットワークやツリー構造モデル)、Versal の計算加速エンジンなどが含まれています。

図5 Versal への機械学習モデルの実装

また、2025 年 8 月 28~30 日にかけて、ハンズオン形式のワークショップも開催し、25 名が参加しました(図 6)。

図6 CEF Summar school for HLS and ML in FPGA

## ● Open-It セミナー

- ① 先端エレクトロニクス DAQ セミナー@Zoom を 2025 年 8 月 4~8 日に開催し、約 70 名が参加しました。

- ② FPGA トレーニングコース(初級)の英語版@KEK を 2025 年 9 月 4~5 日に開催し、6 名が参加しました。

- ③ FPGAトレーニングコース(中級)の英語版@KEK を 2025 年 9 月 8~10 日に開催し、2 名が参加しました。

- ④ FPGA トレーニングコース (初級) @分子研を 2025 年 9 月 11~12 日に開催し、16 名が参加しました。

- ⑤ ASIC トレーニングコース@Zoom を 2025 年 9 月 24~26 日に開催し、17 名が参加しました。