# IIT **の原理と使用方法** ver. 0.2

増田孝彦

July 20, 2007

## Contents

| 1 |      |                       | 3 |

|---|------|-----------------------|---|

|   | 1.1  | Image intensifier     | 3 |

|   | 1.2  | Micro channel plate   | 3 |

|   | 1.3  | C4693 SPL UNIT        | 4 |

|   | 1.4  |                       | 5 |

|   | 1.5  | IIT の性能               | 7 |

|   | 1.5. | 1 カタログ性能値             | 7 |

|   | 1.5. | 2 efficiency          | 7 |

| 2 |      |                       | 9 |

|   | 2.1  | caution               | 9 |

|   | 2.2  | normal mode operation | 9 |

|   | 2.3  | gate mode operation   | 9 |

| 3 |      | CT3300 1              | 0 |

|   | 3.1  | 簡単な使い方                | 0 |

|   | 3.2  | 画像取得プログラム/アルゴリズム      | 1 |

| 4 |      | trigger pulse         | 2 |

## 1 Image intensify tube

## 1.1 Image intensifier

Image intensifier (以下 I.I.) はシングルフォトンレベルという非常に小さい光を、二次元情報を保存したまま検出することのできる検出器である。

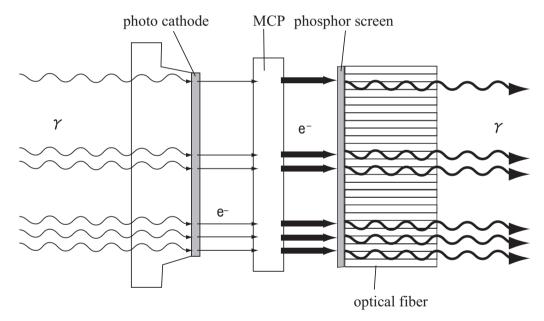

I.I. はセラミック製の真空容器の中に、光を電子に変換する photocathode、電子を増倍する Micro channel plate(以下 MCP)、電子を光に変換する phosphor screen を近接させることにより、周辺部にゆがみのない画像を得るように設計されている。MCP については後述 (1.2)。Fig.1.1 のように、photocathode 上に結像された光は photocathode により光電子へ変換される。このとき放出される光電子数は入射光量に比例する。この電子は photocathode と MCP 入力面 (上流側の面) 間の電圧により加速され MCP の各チャンネルに入射する。MCP の各チャンネル内部は独立した電子増倍部が形成されており、入射した電子は MCP 両端の電圧勾配により数十回の衝突を繰り返すことにより 2 次電子が増加され、MCP の出力端より多数の電子が放出される。MCP によって増倍された電子群は、MCP 出力面 (下流側の面) と phosphor screen 間の電圧により加速されて phosphor screen に衝突する。 Screen では衝突した電子量に応じた光が出力され、MCP1 段の場合、入射した光学像に対して約 3000 倍に増強された出力像が得られる。

Fig. 1.1 I.I. 概要

## 1.2 Micro channel plate

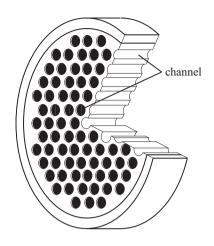

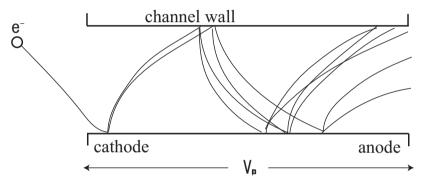

非常に細いチャンネルを多数束ねた構造 (Fig.1.2) をしており、それぞれのチャンネルは独立した 2 次電子増倍器を形成する。MCP に入射した電子は、チャンネル壁に衝突し 2 次電子が放出され、その放出された 2 次電子は、MCP の両端に印加された電圧により加速され、放物線軌道を描き対向する壁に衝突し再び 2 次電子が放出される (Fig.1.3)。この過程がチャンネルに沿って多数回繰り返される結果、出力側より多数の電子が放出されることになる。

Fig.~1.2~~MCP の構造。各チャンネルの直径は  $6\mu m$  である。

Fig. 1.3 MCP 内部で電子が増幅される様子

## 1.3 C4693 SPL UNIT

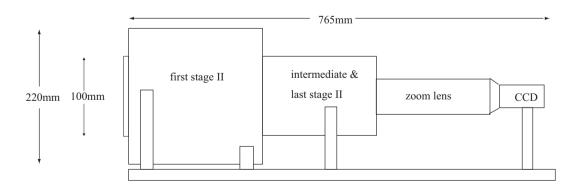

今回用いる Image intensify tube(以下 IIT) は浜松ホトニクス社 C4693 SPL UNIT である。 IIT は Fig. 1.4 に示すように、以下の三段階の I.I. から成り、それぞれに high voltage power supply を持つ。

Fig.~1.4~~C4693~SPL~UNIT

First stage large diameter I.I.

有効半径 50mm でノイズの少ない bialkali photocathode を通して光子を電子に変換し、中の電場によって電子の像を 0.25 倍に縮小し、下流の直径 25mm の phosphor screen(P-24) に出力する。これより下流での像は全て直径 25mm である。

Photocathode の potential は ground に設定されているので、scintillation fiber などを直接接続することが出来、また screen には 20kV の電圧がかけられる。

#### Intermediate stage I.I.

First stage large diameter I.I. の最後の phosphor screen(P-24) から放射された光子をもう一度 bialkali photocathode を通して電子に変換し、MCP を用いて電子数を数千倍に 増幅した後また phosphor screen(P-20) に出力する。この P-20 の残光特性は  $20\mu sec$  で約 10% まで減少する。

この部分は external trigger pulse で I.I. を自動的に起動することが出来る。pulse の幅は 200nsec ~ DC まで対応しており、pulse の立ち上がりから実際に gate が作動するまでにか かる時間は 150nsec である。

#### Last stage I.I.

最後の I.I. には high gain type が使われている。このため、最下流の CCD カメラにかける external trigger が数  $\mu$ sec 遅れても十分な強度の出力をすることが出来る。

Intermediate stage I.I. と Last stage I.I. については MCP の両端の電圧を  $500V \sim 900V$  まで調節することが出来る。

#### 1.4 CCD Camera

本実験では IIT から出力された光学像をインターラインモノクロ CCD カメラを用いて撮影を 行う。

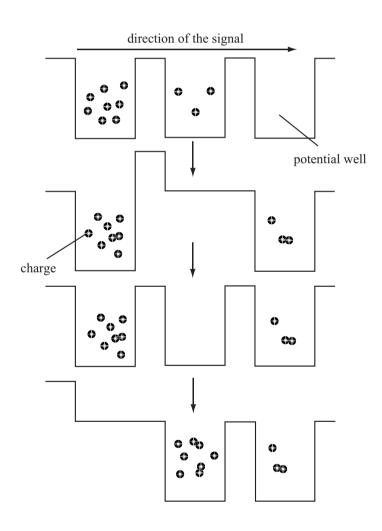

CCD とは"Charge Coupled Device"の略称であり、ビデオカメラ、デジタルカメラなどに広く使用されている半導体素子である。画像を電気信号に変換する際に、受光素子が光から発生した電荷を読み出すために電荷結合素子 (CCD: Charge Coupled Device) と呼ばれる回路素子を用いて転送を行うことからこう呼ばれる。CCD は、他の撮像素子に比べて相対的に感度が高く、ノイズが少ないという特徴を持つ。CCD は MOS 構造半導体素子の一種で、シリコン基盤表面の酸化膜上に多数の電極を設け、各電極に隣同士で異なる電圧を与えることにより potential well を作り出し、これを利用して電荷を保持できるようにしたものである。各電極に加える電圧を適切に制御することにより各素子の電荷が隣の素子にいっせいに転送される。これにより各素子が保持する画素ごとの電荷をバケツリレー式に順次外部に取り出すことができる。(Fig.1.5) この性質を利用して一列の端から入力した電荷を素子数分の転送回数に相当する遅延を持たせて反対側の端から取り出せば、遅延線(ディレイライン)として動作させることができる。

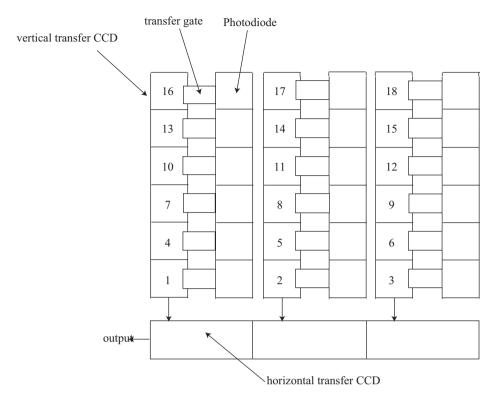

インターライン CCD カメラは、受光部のフォトダイオードと電荷転送部の垂直転送 CCD を一列ごとに交互に配置し、垂直 CCD 列の端部を水平転送 CCD の各素子に接続して全体として櫛形に配置した構造である。各転送用 CCD は光電変換を行わないように遮光膜で覆ってある。また、各画素のフォトダイオードと画素に対応する垂直 CCD の各素子に間にはアナログスイッチとして働くトランスファゲートが置かれている。読み出しは一例として次のようにして行う。

- 1. トランスファゲートを閉じておく。

- 2. フォトダイオードを感光し、電荷を蓄積する。

- 3. トランスファゲートを開き、フォトダイオードから各垂直転送 CCD に電荷をいっせいに転送する。

- 4. トランスファゲートを閉じる。

- 5. 各垂直転送 CCD の電荷を 1 回分転送し、各列の端部にあたる画素の電荷を水平転送 CCD に移送する。

- 6. 水平転送 CCD に順次転送パルスを与えて全水平画素を出力する。

#### 7.5 に戻って垂直転送 CCD の全画素を読み出すまで繰り返す。

これによりすべての全エリアの画素が順次走査されたことになる。(Fig.1.6) 動画をとるために必要なフレーム数が、この走査速度では足りない場合垂直転送用 CCD を間引いて、交互に電荷を転送する方式が取られる。これをインターレース式を呼ぶ。

CCD カメラから送られてくる信号はアナログなので、 $Video\ capture\ board$ (の上に設置された ADC) を通すことでデジタル信号に変換し、PC に保存するという流れになる。

なお実験に使用する CCD カメラは浜松ホトニクス製インターライン式 2/3 型 CCD カメラ C3077、Video capture board は CYBERTEK 製 Bus\_master PCI monochrome image processing board "CT-3300A" である。この CCD カメラは 2:1 インターレース式画像転送方式となって いる。

Fig. 1.5 受光素子ごとに作られた potential well に捕らえられた電荷を、電圧を適当に調整することによって素子ごとの電荷量を変えずに順次移動させていく。

Fig. 1.6 インターライン CCD の仕組み。図中の垂直転送用 CCD にふってある番号順に読み込んでいくことになる。

## 1.5 IIT の性能

#### 1.5.1 カタログ性能値

Table. 1.1 C4693 SPL UNIT のカタログ性能値

| 感応波長領域                                | 350-650 nm       |

|---------------------------------------|------------------|

| photocathode 量子効率 (First I.I.)        | 18% (430 nm)     |

| photocathode 量子効率 (Intermediate I.I.) | 10% (450 nm)     |

| photocathode 量子効率 (Last I.I.)         | 10% (550 nm)     |

| 増幅率 (First I.I.)                      | 10 ~             |

| 増幅率 (Intermediate & Last I.I.)        | ~ 3000           |

| ノイズ                                   | 2000  counts/sec |

#### 1.5.2 efficiency

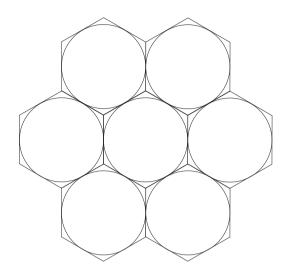

IIT C4693 SPL UNIT の受光面は円柱状の optical fiber が多数敷き詰められて、直径 100mm の円を形成している。したがってもし photon が fiber の隙間に入ってしまった場合、その photon は検出されない。すなわち入射面に対する fiber の開口部の面積の割合で efficiency が決まる。Fiber は最密に敷き詰められているので、Fig. 1.7 からわかるようにその面積比は

$$\frac{\pi r^2}{2\sqrt{3}r^2} \simeq 91\% \tag{1.1}$$

Fig. 1.7 IIT 入射面の様子

である。さらに初段 I.I. の中の photocathode の量子効率が掛け合わされる。この量子効率は Table.1.1 のカタログ値  $18\%(430\mathrm{nm})$  で、可視光全体の平均としては 10% 程度である。さらに First I.I. の増幅率が 10 倍程度で Intermediate I.I. の中の photo cathode の量子効率が最大 10% なので平均して 5% 程度になると考えられる。その後は I.I. で十分に増幅されるため efficiency には影響しない。これらを考えると IIT 全体の efficiency は 5% 以下であるといえる。

## 2 IIT の使用方法

#### 2.1 caution

• Storage

first stage I.I. の光電面に長時間光が当たると光電面が劣化するので、使わないときは入射窓を完全に覆っておく。

• AC cable

3 台の電源にそれぞれ 3 ピンタイプの AC 電源ケーブルをつなぐ。もしコンセントが 2 穴タイプの場合は、電源本体裏面の ground terminal にアースを接続する。

fuse check

電源本体裏面にヒューズホルダーがあるので、ドライバーで開けて中のヒューズが導通しているかを確認する。(初回起動時のみで OK)

• warm up

本来の性能を出すためには15分程度のwarm upが必要になる。

switch

ダイヤルが 0.00 以外のときに電源を入れたり切ったりしない。また normal mode と gate mode を切り替える際は必ず電源を切っておく。

#### 2.2 normal mode operation

- 1. 電源 OFF、ダイアル 0.00、モード切り替えスイッチが normal になっていることを確認する。

- 2. CCD 直前のレンズの絞りを完全に開く。また、ピントを一番近くに合わせる。

- 3. CCD の電源を入れ、モニターをつける。CCD からの画像が出力されていることを確認する。

- 4. CCD を取り付け、完全に遮光する。

- 5. last stage I.I.、intermediate stage I.I. の順に電源を入れ、pilot lamp がついていることを確認する。

- 6. 両方のダイアルを 6.00 までゆっくり上げる。

- 7. first stage I.I. の電源を入れ、pilot lamp がついていることを確認。

- 8. モニターに何も映ってなければ、warm up も兼ねてしばらく待つ (5-10) 分くらい)。

- 9. 必要な光量になるまでダイアルを回す。

- 10. がんばって測定する。

- 11. intermediate stage I.I.、last stage I.I の順にダイアルを 0.00 まで落とす。

- 12. first intermediate last の順に電源を落とす。

- 13. CCD の電源を落とす。

## 2.3 gate mode operation

- 1. まず normal mode operation を行い、IIT が正常に動作しているかを確認する。

- 2. 電源を落とし、gate mode に切り替える。

- 3. 一旦 DC でトリガー用の TTL signal を供給する。

- 4. normal mode と同じ要領で電源を入れる。ただしゲインを調整する場合は、まず last stage I.I. を 9.00 まで上げて、それでも足りなければ intermediate stage I.I. を調整する。

- 5. gate signal の幅を調整したら、いっぱい測定する。

- 6. normal mode と同じ要領で電源を落とす。

## 3 CT3300

#### 3.1 簡単な使い方

- 1. 大量の画像ファイルが生成されるので、run 毎に新しい folder を作っておく。

- 2. folder の中に CT3300.exe を移動させる。

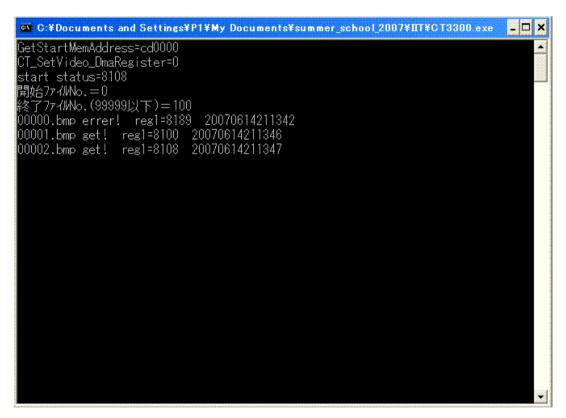

- 3. CT3300.exe を起動させ、開始ファイルナンバーを整数 (0 99999) で入力し、終了ファイルナンバー ( 99999) も整数値で入力する。小数や 100000 以上の整数には対応していないので注意。

- 4. enter を押したら取り込み開始。

- 5. 途中でやめる場合は e か q を押す。window の右上の閉じるボタンで止めない。万一閉じるボタンで止めてしまった場合は PC 自体の再起動が必要になる。(ドライバが開きっぱなしになるため)

- 6. トリガが入力されるたびに、取得ファイル名、レジストリ値、取得時間が表示される。これ は同じフォルダ内に生成されるログファイルにも書き込まれている。

- 7. レジストリ値の下一桁が 0 か 8 以外の場合はタブルトリガなどでうまく取得できていない ので注意。

- 8. 取得が終わったら自動的に閉じる。

Fig. 3.1 CT3300.exe の画面例

## 3.2 画像取得プログラム/アルゴリズム

CT3300A を動作させるアルゴリズムを以下に記す。ソースファイル中で [CT...] で始まる関数は本ドライバ特有の関数であり、CT3300.lib や CT3300.dll に定義されている。

全ての作業はまず CT3300 のドライバを開くことから始める。GetStartMemAddress 関数で windows 上で作業する仮想メモリのアドレスを取得し、 $SetVideo\_DmaRegister$  関数でレジスタの初期値をセットする。さらに外部トリガモード、取り込みフレーム数 1 枚、転送バッファの先頭アドレスを設定した後、連写枚数を適宜入力できるようにしている。

外部トリガ信号が入力されているかを確かめるために 15 msec ごとに  $CT_{INB}$  でドライバを確認し、その戻り値によって判断する。トリガが入力されてなければそれを繰り返し行い、もしトリガが入力されていればメモリに書き込む時間だけ入力を待機させ、csavedib 関数でデータを bit map graphics にエンコードして保存する。これを入力済みの連写枚数回繰り返す。途中で停止させたい場合には [q] または [e] を入力する。

終了したら Capture を止め、ドライバをクローズして終了させる。

## 4 trigger pulse

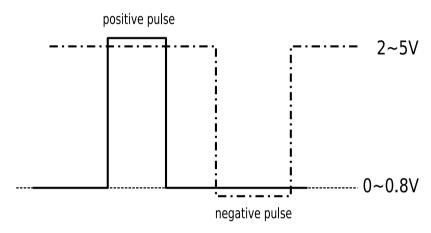

trigger pulse はシンチレーションカウンタからのコインシデンスで作る予定。コインシデンスからの出力を各種 NIM モジュールで幅、タイミング等を調整し、最後に LEVEL ADAPTER で IIT 用の positive(正論理)TTL signal と CT3300 用の negative(負論理)TTL signal を出力する。

IIT の gate が開いている時間は、IIT に入れる trigger pulse の幅に等しい(ただし 150nsec 遅れる)。Pulse の幅が狭いと十分な光量が得られないが、広すぎるとノイズが増えるので調整が必要になる。また約 10kHz を超えると pulse を認識できなくなるため、Clock generator などで test pulse を作る際は周波数を低めにしておく。

CCD は 1 秒間に 30 フレームの画像を撮影している。2:1 インターレース式なので 1 フレームは、2 フィールドから成っておりそれぞれ順番に転送されてくる。CT3300 は trigger pulse が入力されるとフレームが切り替わるまで待機し、切り替わった後のフレームから保存し始め、1 フレーム保存するか pulse が消えると保存を止める。したがって CT3300 に入力する trigger pulse 幅は 60 msec 以上に設定しておく必要がある。

Fig. 4.1 TTL signal。実線が正論理、破線が負論理。