# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2006-115274 (P2006-115274A)

(43) 公開日 平成18年4月27日(2006.4.27)

| (51) Int.C1. |               |           | F I  |       |   | テーマコード (参考) |

|--------------|---------------|-----------|------|-------|---|-------------|

| нозк         | <i>5/13</i> 5 | (2006.01) | нозк | 5/135 |   | 2F085       |

| G04F         | 10/06         | (2006.01) | GO4F | 10/06 |   | 5 J O O 1   |

| нозк         | 5/ <b>2</b> 6 | (2006.01) | нозк | 5/26  | Z | 5 J O 3 9   |

|                       |                                                          | 審査請認     | 求 未請求 請求項の数 3 OL (全 9 頁)                  |

|-----------------------|----------------------------------------------------------|----------|-------------------------------------------|

| (21) 出願番号<br>(22) 出願日 | 特願2004-301234 (P2004-301234)<br>平成16年10月15日 (2004.10.15) | (71) 出願人 | 504151365<br>大学共同利用機関法人 高エネルギー加速<br>器研究機構 |

|                       |                                                          | (74)代理人  | 茨城県つくば市大穂1番地1<br>100072051<br>弁理士 杉村 興作   |

|                       |                                                          | (74)代理人  | 100100125<br>弁理士 高見 和明                    |

|                       |                                                          | (74)代理人  | 100101096<br>弁理士 徳永 博                     |

|                       |                                                          | (74)代理人  | 100086645<br>弁理士 岩佐 義幸                    |

|                       |                                                          | (74)代理人  | 100107227<br>弁理士 藤谷 史朗                    |

|                       |                                                          |          | 最終頁に続く                                    |

(54) 【発明の名称】 2つのPLLを用いた微小時間差回路及び時間測定回路

# (57)【要約】

【課題】1桁以上時間分解能を向上させることができる 微小時間差回路及び時間測定回路を提供する。

【解決手段】所定の基準クロック信号を受け、第1発振 周波数を発生する電圧制御発振回路を具える第1位相同 期ループ回路と、前記第1位相同期ループ回路と同じ基 準クロック信号を受け、前記第1発振周波数と異なる第 2発振周波数を発生する電圧制御発振回路を具える第2 位相同期ループ回路とを具え、前記第1位相同期ループ 回路と前記第2位相同期ループ回路の出力信号の遅延時 間差から微小時間を得る。

# 【選択図】図3

#### 【特許請求の範囲】

# 【請求項1】

所定の基準クロック信号を受け、第1発振周波数を発生する電圧制御発振回路を具える第1位相同期ループ回路と、前記第1位相同期ループ回路と同じ基準クロック信号を受け、前記第1発振周波数と異なる第2発振周波数を発生する電圧制御発振回路を具える第2位相同期ループ回路とを見え、前記第1位相同期ループ回路と前記第2位相同期ループ回路の出力信号の遅延時間差から微小時間を得ることを特徴とする微小時間差回路。

# 【請求項2】

第1発振周波数を発生する電圧制御発振回路を具える第1位相同期ループ回路と、前記第1位相同期ループ回路と同じ基準クロック信号を受け、前記第1発振周波数と異なる第2発振周波数を発生する電圧制御発振回路を具える第2位相同期ループ回路とを具え、前記第1位相同期ループ回路及び前記第2位相同期ループ回路の各々に関して、出力信号が各々次に入力されるように直列に接続された複数の可変遅延回路から成る遅延線を具え、各遅延線における各々の可変遅延回路は、関係する位相同期ループ回路の出力信号によって遅延時間を制御され、各遅延線における最初の可変遅延回路は、時間差を得ようとする2つの信号のうち一方を受け、各々の遅延線において同時に変化する可変遅延回路の出力を見つけることにより、前記2つの信号の時間差を決定することを特徴とする時間測定回路。

#### 【請求項3】

複数N1段の遅延回路から成る第1電圧制御発振回路と、前記第1電圧制御発振回路の 出力を受け、その周波数を複数M1倍する第1分周回路と、前記第1分周回路の出力と基 準 ク ロ ッ ク と を 受 け 、 こ れ ら の 信 号 の 位 相 差 を 前 記 第 1 電 圧 制 御 発 振 回 路 に 帰 還 す る 位 相 周波数検出器とを具える第1位相同期ループ回路と、複数N2段の遅延回路から成る第2 電圧制御発振回路と、前記第2電圧制御発振回路の出力を受け、その周波数を複数M2倍 す る 第 2 分 周 回 路 と 、 前 記 第 2 分 周 回 路 の 出 力 と 基 準 ク ロ ッ ク と を 受 け 、 こ れ ら の 信 号 の 位相差を前記第2電圧制御発振回路に帰還する位相周波数検出器とを具える第2位相同期 ル ー プ 回 路 と 、 外 部 信 号 を 受 け る と 共 に 、 前 記 第 1 分 周 回 路 の 出 力 を ク ロ ッ ク 入 力 信 号 と して受け、粗時間測定を行うカウンタ回路と、前記外部信号を受けると共に、前記第1電 圧制御発振回路における遅延回路の各段の出力信号を受け、微細時間測定を行うラッチ及 び 位 相 選 択 回 路 と を 具 え 、 前 記 第 1 位 相 同 期 ル ー プ 回 路 及 び 前 記 第 2 位 相 同 期 ル ー プ 回 路 の各々に関して、出力信号が各々次に入力されるように直列に接続された複数の可変遅延 回路から成る第1及び第2遅延線を具え、関係する位相同期ループ回路の出力信号によっ て遅延時間を制御され、前記第1遅延線における最初の可変遅延回路は、前記ラッチ及び 位相選択回路により決定された、前記外部信号に立ち上がりに最も近いタイミングの前記 第1電圧制御発振回路における遅延回路の段の出力信号を受け、前記第2遅延線における 最 初 の 可 変 遅 延 回 路 は 、 前 記 ラ ッ チ 及 び 位 相 選 択 回 路 に よ り 、 前 記 第 1 及 び 第 2 遅 延 線 内 で 前 記 第 1 遅 延 線 が 受 け た 信 号 を 追 い 抜 け る よ う に 遅 延 を 調 整 さ れ た 前 記 外 部 信 号 を 受 け 、 前 記 第 1 及 び 第 2 遅 延 線 内 の ど の 遅 延 回 路 の 出 力 に お い て 信 号 の 到 着 時 間 が 逆 転 し た か を調べることによって超微細時間測定を行うことを特徴とする時間測定回路。

#### 【発明の詳細な説明】

# 【技術分野】

#### [00001]

本発明は、高精度時間計測に関し、特に微小時間差回路と、これを使用する時間測定回路に関する。

### 【背景技術】

# [0002]

科学計測機器、自動車や航空機等の距離測定装置、TOF(Time Of Flight)による元素分析器等におけるデジタル回路においては、入力信号の時間を高精度に測定する必要がある。

# [0003]

10

20

30

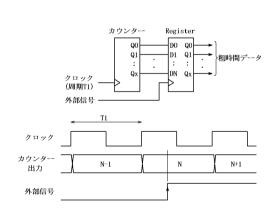

一般に、デジタル回路において時間を測定する最も簡単な方法は、図1に示すようにクロックを用いてカウンタを動作させ、測定したい信号が到達したときにその時のカウンタの値をレジスタに取り込む方法である。しかしながら、この場合の時間分解能(最小時間単位)は、クロックの周期で決まってしまい、例えば100MHzのクロックを使用した場合では10nsとなる。

## [0004]

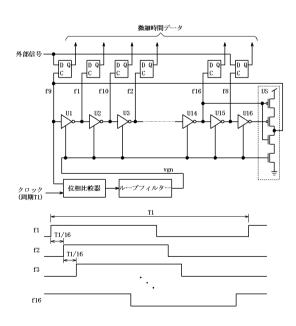

基準クロック周期よりも短い時間単位の時間測定を行うために、例えば、特開平7-283697号「電圧制御発振回路及びこれを用いた信号検出器」明細書に記載されての電ような、PLL(Phase Locked Loop:位相同期ループ)回路内の電圧制御発振回路を用い、発振周期の整数N分の1の遅延信号を得る回路が開発されている。図2は、このような回路の回路図である。この図に示す例は、16段の遅延回路のこのの反転回路U1~U16及びUSにより電圧制御発振回路を構成し、PLL回路から得の回路は、通常奇数段の位相反転回路を用いなければ発振を起こせないところを、偶数段でおように工夫したもので、信号の立ち上がりがf1 f2 f3 ... f16 f1の順番で変化し、基準クロックの16分の1の時間間隔を持った立ち上がり信号を得ることができる。この場合、時間分解能は発振周期のN分の1とすることができるに、1段の反転回路の遅延時間よりも分解能を上げることはできない。通常のCMOS回路では、1段の反転回路の遅延時間は0.2ns程度なので、2段の反転回路(=1段の遅延回路)の遅延時間は0.4ns程度となる。

【特許文献 1 】特許第2663397号公報

【発明の開示】

【発明が解決しようとする課題】

[0005]

上述したような従来技術の回路でさらに時間分解法を上げるためには、より高速の集積回路プロセス技術を用い、クロック周波数を上げること等が必要となる。しかしながら、ゲートの遅延時間の減少には当然ながら限界があり、消費電力が増えたり、製造コストが高額になってしまうといった問題があった。

[0006]

本発明の目的は、上述したような従来技術の問題を克服し、 1 桁以上時間分解能を向上させることができる微小時間差回路及び時間測定回路を提供することである。

【課題を解決するための手段】

[0007]

本発明による微小時間差回路は、所定の基準クロック信号を受け、第1発振周波数を発生する電圧制御発振回路を具える第1位相同期ループ回路と、前記第1位相同期ループ回路と同じ基準クロック信号を受け、前記第1発振周波数と異なる第2発振周波数を発生する電圧制御発振回路を具える第2位相同期ループ回路とを具え、前記第1位相同期ループ回路と前記第2位相同期ループ回路の出力信号の遅延時間差から微小時間を得ることを特徴とする。

[0008]

本発明による時間測定回路は、第1発振周波数を発生する電圧制御発振回路を具える第1位相同期ループ回路と、前記第1位相同期ループ回路と同じ基準クロック信号を受け、前記第1発振周波数と異なる第2発振周波数を発生する電圧制御発振回路を具える第2位相同期ループ回路とを具え、前記第1位相同期ループ回路及び前記第2位相同期ループ回路の各々に関して、出力信号が各々次に入力されるように直列に接続された複数の可変遅延回路から成る遅延線を具え、各遅延線における各々の可変遅延回路は、関係する位相同期ループ回路の出力信号によって遅延時間を制御され、各遅延線における最初の可変遅延回路は、時間差を得ようとする2つの信号のうち一方を受け、各々の遅延線において同時に変化する可変遅延回路の出力を見つけることにより、前記2つの信号の時間差を決定することを特徴とする。

20

30

#### [0009]

本発明による他の時間測定回路は、複数N1段の遅延回路から成る第1電圧制御発振回 路と、前記第1電圧制御発振回路の出力を受け、その周波数を複数M1倍する第1分周回 路と、前記第1分周回路の出力と基準クロックとを受け、これらの信号の位相差を前記第 1電圧制御発振回路に帰還する位相周波数検出器とを具える第1位相同期ループ回路と、 複数N2段の遅延回路から成る第2電圧制御発振回路と、前記第2電圧制御発振回路の出 力を受け、その周波数を複数M2倍する第2分周回路と、前記第2分周回路の出力と基準 クロックとを受け、これらの信号の位相差を前記第2電圧制御発振回路に帰還する位相周 波数検出器とを具える第2位相同期ループ回路と、外部信号を受けると共に、前記第1分 周回路の出力をクロック入力信号として受け、粗時間測定を行うカウンタ回路と、前記外 部信号を受けると共に、前記第1電圧制御発振回路における遅延回路の各段の出力信号を 受け、微細時間測定を行うラッチ及び位相選択回路とを具え、前記第1位相同期ループ回 路 及 び 前 記 第 2 位 相 同 期 ル ー プ 回 路 の 各 々 に 関 し て 、 出 力 信 号 が 各 々 次 に 入 力 さ れ る よ う に直列に接続された複数の可変遅延回路から成る第1及び第2遅延線を具え、関係する位 相同期ループ回路の出力信号によって遅延時間を制御され、前記第1遅延線における最初 の可変遅延回路は、前記ラッチ及び位相選択回路により決定された、前記外部信号に立ち 上がりに最も近いタイミングの前記第1電圧制御発振回路における遅延回路の段の出力信 号を受け、前記第2遅延線における最初の可変遅延回路は、前記ラッチ及び位相選択回路 により、前記第1及び第2遅延線内で前記第1遅延線が受けた信号を追い抜けるように遅 延を調整された前記外部信号を受け、前記第1及び第2遅延線内のどの遅延回路の出力に おいて信号の到着時間が逆転したかを調べることによって超微細時間測定を行うことを特 徴とする。

# 【発明の効果】

# [ 0 0 1 0 ]

従来の集積回路中のPLL素子を使用した時間測定回路では、遅延回路の遅延時間以下の時間精度を得ることはできなかった。本発明によれば、2つの電圧制御発振回路で使用される遅延回路のそれぞれの遅延時間は従来技術と同程度のものであっても、その時間差は、遅延時間のさらに整数N分の1にすることができる。これにより、より微小な時間差の信号発生や時間測定を行うことができるようになる。

【発明を実施するための最良の形態】

### [0011]

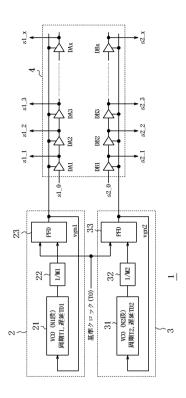

図3は、本発明による微小時間差回路の構成の一例を示すブロック図である。微小時間差回路1は、第1位相同期ループ(PLL)回路2と、第2PLL回路3と、二重遅延ライン部4とを具える。

# [0012]

第1PLL回路2は、電圧制御発振回路(VCO)21と、分周回路22と、位相周波数検出器(PFD)23とを具える。VCO21は、N1段の遅延回路で構成され、その発振出力信号は分周回路22によりM1分の1の周波数に分周され、PFD23に入力される。PFD23には周期T0の基準クロックも入力され、PFD23はこれら2つの入力信号の位相差を検出し、位相差電圧信号vgn1をVCO21に帰還する。vgn1を変化させることにより、分周回路22の出力信号を基準クロックに周波数位相同期させる。このときのVCO21の出力の周期をT1とすると、

T 1 = T 0 / M 1 (1)

となる。また、 V C O 2 1 の 1 段あたりの遅延時間 T D 1 は、 V C O 2 1 が N 1 段の遅延 回路から成ることから、

TD1 = T1 / N1 (2)

20

30

(5)

となる。

# [0013]

第2 P L L 回路 3 は、第1 P L L 回路 2 と同様の構成で、電圧制御発振回路(VCO)3 1 と、分周回路 3 2 と、位相周波数検出器(P F D) 3 3 とを具える。VCO3 1 は、N 2 段の遅延回路で構成され、その出力は分周回路 3 2 によりM 2 分の 1 の周波数に分周され、P F D 3 3 に入力される。P F D 3 3 には第1 P L L 回路 2 の P F D 2 3 に入力されるのと同じ周期 T 0 の基準クロックも入力され、P F D 3 3 はこれら 2 つの入力信号の位相差を検出し、位相差電圧信号 V g n 2 を V C O 3 1 に帰還する。 V g n 2 を変化させることにより、分周回路 3 2 の出力信号を基準クロックに周波数位相同期させる。このときの V C O 3 1 の出力の周期を T 2 とすると、

T 2 = T 0 / M 2 (3)

となる。また、 V C O 3 1 の 1 段あたりの遅延時間 T D 2 は、 V C O 3 1 が N 2 段の遅延 回路から成ることから、

TD2 = T2 / N2 (4)

となる。

[0014]

TD2とTD1の時間差 Tは、式(2)及び(4)より、

T = T D 2 - T D 1= T 2 / N 2 - T 1 / N 1

となる。これに式(1)、(2)及び(3)を代入すると、

$T = T 0 / (M 2 \cdot N 2) - T 1 / N 1$ =  $(T 1 \cdot M 1) / (M 2 \cdot N 2) - T 1 / N 1$ =  $(T 1 / N 1) ((N 1 \cdot M 1) / (M 2 \cdot N 2) - 1)$

となる。ここで簡単のためN1=N2=M2=N、M1=N+1とすると、

$T = T 1 / (N \cdot N) = T D 1 (1 / N)$  (5)

となり、VCO21の発振周期T1のNの二乗分の1、遅延回路の遅延時間TD1のN分の1の時間差が得られる。

[0015]

同様に、N1=N2=M2=N、M1=N+2とすると、

T = T D 1 (2 / N)

となり、TD1のN分の2の時間差が得られる。他に、N1、N2、M1、M2の値を適当に選ぶことで、任意の Tを実現することも可能である。

[0016]

このように従来の回路ではTD1の遅延しか得られなかったものが、本発明による微小時間差回路により、その値のさらに整数N分の1の遅延が得られる。特に、Nを2の累乗に選べば、後段のデジタル処理を非常に容易にすることができる。例えば式(5)で、N=16とすると、T1、TD1、 Tがそれぞれ16倍ずつ違う値を持つことになる。

[0017]

50

10

20

30

20

30

40

50

このようにして得られた時間差を実際に利用するために、二重遅延ライン部 4 が使用される。 D A x 、 D B x (x = 1 , 2 , 3 . . . )は、 V C O 2 1 、 V C O 3 1 で使用される可変遅延回路と同じもので、反転素子 2 段より成る。このとき、信号 s 1 \_\_ x と s 2 \_\_ x が同時に変化する (T 1 x = T 2 x )タップ x を見いだす回路を用いれば、 s 1 \_\_ 0 と s 2 0 の時間差を T の精度で知ることができる。

#### [0018]

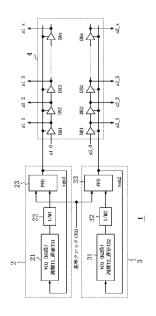

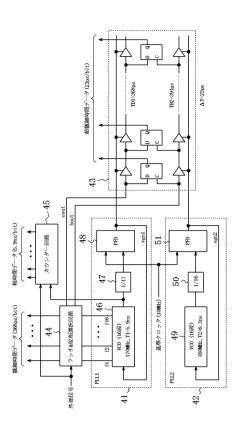

図3に示したような微小時間差回路によって得られる微小時間差信号を用いて超微細な時間測定を行うことができるが、この回路だけで広い時間範囲をカバーすると、回路規模が大きくなりすぎ、また時間精度も悪くなるので、通常は、図1及び図2において示した従来例のように、カウンタや電圧制御発振回路と組み合わせた回路構成を取るのが好適である。図4は、このような本発明による時間測定回路の構成の一例を示すブロック図である。本時間測定回路は、第1PLL回路41と、第2PLL回路42と、二重遅延ライン部43と、ラッチ及び位相選択回路44と、カウンタ回路45とを具える。

# [ 0 0 1 9 ]

第 1 P L L 回路 4 1 及び第 2 P L L 回路 4 2 は、図 3 に示す第 1 P L L 回路 2 及び第 2 P L L 回路 3 と同様の構成であってもよく、これらが具える V C O 4 6 、分周回路 4 7 、 P F D 4 8 、 V C O 4 9 、分周回路 5 0 及び P F D 5 1 は、図 3 に示す V C O 2 1 、分周回路 2 2 、 P F D 2 3 、 V C O 2 1 、分周回路 2 2 及び P F D 2 3 と同様のものであってもよい。

### [0020]

本実施例においては、例として、第1PLL回路41及び第2PLL回路42に用いる基準クロックとして10MHzのクロックを使用する。この周波数を第1PLL回路41によりまず17倍の170MHzに上げる。この170MHzのクロックを使用して、カウンタ回路45で、分解能5.9ns(=1/170MHz)の粗時間測定を行う。

#### [ 0 0 2 1 ]

次に、第1 P L L 回路 4 1 を構成する 1 6 段より成る V C O 4 6 から得られる遅延信号 出力 f 1 ~ f 1 6 を用いて、ラッチ及び位相選択回路 4 4 において、分解能 3 6 8 p s ( = 5 . 9 n s / 1 6 ) の微細時間測定を行う。

# [0022]

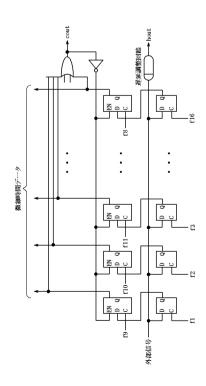

# [ 0 0 2 3 ]

次に、微細時間のラッチと、二重遅延ライン部43に供給するための信号を第1VCO41の出力信号から取り出すための位相選択とを行う、ラッチ及び位相選択回路44を説明する。図5は、ラッチ及び位相選択回路の構成の一例を示す回路図である。まず、外部信号を第1VCO46からのf1~f16信号によりフリップフロップにラッチする。1段目のフリップフロップの出力は、外部信号の変化のタイミングにより、短時間不安定になることがあるので、1段目のクロックと位相を180度ずらした2段目のフリップこロップにより安定にラッチさせる。この出力が微細時間データとなり、この論理和をとることにより、外部信号の立ち上がり後の最も近いタイミング(から180度遅れた)の信号をf1~f16の中から選択することができる(cout信号がhout信号を11~F16の中から選択することができる。この遅延調整では、図3のDA×、DB×と同様の遅延回路を用いることができる。

# [0024]

最後に、二重遅延ライン部43内のフリップフロップ出力をラッチし、どのタップ位置

において信号の到着時刻が逆転したかを調べることにより、超微細時間測定が行われる。

### [0025]

上記実施例において示した数値は説明を明瞭にするための単なる例であり、本発明はこれらに限定されないことは当然である。

# 【図面の簡単な説明】

- [0026]

- 【図1】従来のカウンタによる時間測定例を説明する図である。

- 【図2】従来のPLLを用いた時間測定回路を説明する図である。

- 【図3】本発明による微小時間差回路の構成の一例を示すブロック図である。

- 【図4】本発明による時間測定回路の構成の一例を示すブロック図である。

- 【図5】ラッチ及び位相選択回路の構成の一例を示す回路図である。

### 【符号の説明】

- [0027]

- 1 微小時間差回路

- 2、41 第1PLL回路

- 3、42 第2PLL回路

- 4、43 二重遅延ライン部

- 21, 31, 46, 49 VCO

- 2 2 、 3 2 、 4 7 、 5 0 分周回路

- 23、33、48、51 PFD

- 4 4 ラッチ及び位相選択回路

- 45 カウンタ回路

【図1】

10

【図3】

【図5】

# フロントページの続き

(74)代理人 100114292

弁理士 来間 清志

(74)代理人 100119530

弁理士 冨田 和幸

(72)発明者 新井 康夫

茨城県つくば市倉掛742-4

F ターム(参考) 2F085 AA05 CC10 GG06 GG19 GG21 GG23 GG24

5J001 BB05 BB09 BB12 BB14 BB20 BB21 BB24 CC03 DD00 DD04 5J039 JJ07 JJ18 KK01 KK09 KK10 KK13 KK20 KK23 KK27 MM16